Fターム[5F110DD21]の内容

Fターム[5F110DD21]に分類される特許

81 - 100 / 538

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

縦型電界効果トランジスタとその製造方法及び電子機器

【課題】縦型電界効果トランジスタとその製造方法及び電子機器において、基材の材料の選択の幅を広げること。

【解決手段】基材1と、基材1の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極2と、基材1の上に形成され、第1の電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、第1の絶縁膜3の上に形成され、開口12を備えた第2の絶縁膜8と、開口12の横の第2の絶縁膜8の上に形成され、ソース電極とドレイン電極のうちの他方となる第2の電極10と、開口12の側面に形成されたゲート絶縁膜16と、第1の電極2、第2の電極10、及びゲート絶縁膜16上に形成され、酸化物半導体を材料とするチャネル17とを有する縦型電界効果トランジスタによる。

(もっと読む)

半導体化合物

【課題】空気安定性、良好な溶解度、および高い移動度を持つ有機薄膜トランジスタ用半導体を提供する。

【解決手段】特定構造のチアキサンテノチアキサンテン化合物を活性層として用いる。チアキサンテノチアキサンテン化合物は主に結晶性または液晶である。この化合物は、空気安定性、良好な溶解度、および高い移動度を確実にするように設計される。有機薄膜トランジスタは一般に、基板20上に、ゲート電極30、ソース電極50およびドレイン電極60、ゲート電極をソースおよびドレイン電極と分離する電気絶縁ゲート誘電体層40、およびゲート誘電体層と接触し、ソースおよびドレイン電極を架橋する半導体層70を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

貼り合わせ基板及びその製造方法

【課題】中空構造等を作製するためのエッチング工程とガラス基板等他の部材の貼り付け工程を必要としない簡単な工程で、センサー等を作製するための貼り合わせ基板を製造する方法、及び構造強度の問題となる中空構造を形成しなくとも、センサー等の作製に用いることができる多孔質領域を有する貼り合わせ基板を提供する。

【解決手段】ベース基板1の貼り合わせ面に部分的に多孔質領域3を形成する工程と、ボンド基板4の貼り合わせ面に絶縁膜2を形成する工程と、絶縁膜2を介してベース基板1とボンド基板4を貼り合わせる工程と、貼り合わせられたボンド基板4を薄膜化して薄膜層を形成する工程とを有する。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

スパッタリングターゲット、スパッタリングターゲットの作製方法および半導体装置の作製方法

【課題】酸窒化物膜を作製する成膜技術を提供する。また、その酸窒化物膜を用いて信頼性の高い半導体素子を作製する。

【解決手段】窒化インジウム、窒化ガリウム、窒化亜鉛の少なくとも1つを原料の一とし、これと、酸化インジウム、酸化ガリウム、酸化亜鉛の少なくとも1つと混合して窒素雰囲気中で焼結したインジウムとガリウムと亜鉛を有する酸窒化物よりなるスパッタリングターゲットを用いて酸窒化物膜を作製することにより、必要な濃度の窒素を含んだ酸窒化物膜が得られる。得られた酸窒化物膜はトランジスタのゲートやソース電極、ドレイン電極等に用いることができる。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

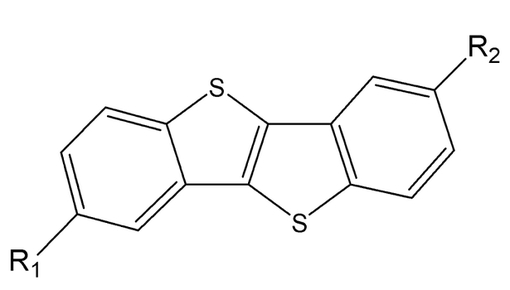

低分子半導体

【課題】高い移動度および良好な膜形成性を示す半導体化合物を提供する。

【解決手段】下式の低分子半導体。

〔R1、R2は、アルケニル、アルキニル、アリール、アルコキシ、アルキルチオ等〕

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけられた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとして機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面を有するディスプレイを実現するものである。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】絶縁表面上に膜厚が1nm以上10nm以下の第1の材料膜(六方晶の結晶構造を有する膜)を形成し、第1の材料膜を核として、六方晶の結晶構造を有する第2の材料膜(結晶性酸化物半導体膜)を形成し、第1の材料膜と第2の材料膜の積層を形成する。第1の材料膜としては、ウルツ鉱型結晶構造を有する材料膜(例えば窒化ガリウム、或いは窒化アルミニウム)、或いはコランダム型結晶構造を有する材料膜(α−Al2O3、α−Ga2O3、In2O3、Ti2O3、V2O3、Cr2O3、或いはα−Fe2O3)を用いる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

表示装置

【課題】

表示装置の高解像度化や小型化、さらには画素の開口率の向上を行った場合でも、半導体層に入射する光を効果的に遮断し、ホトコン電流による表示品質の低下を防止することが可能な表示装置を提供すること。

【解決手段】

前記基板上に、第1絶縁膜と、ゲート電極と、ゲート電極の上層に形成された第2絶縁膜と、前記第2絶縁膜の上層に形成された半導体層とが積層され、前記第1絶縁膜は開口部を有し、前記ゲート電極は、前記開口部に倣って形成された窪みを有し、前記半導体層の全部、又は前記半導体層の端部は、平面的に見て前記窪みと重畳していることを特徴とする。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

81 - 100 / 538

[ Back to top ]