Fターム[5F110EE03]の内容

Fターム[5F110EE03]に分類される特許

21 - 40 / 5,376

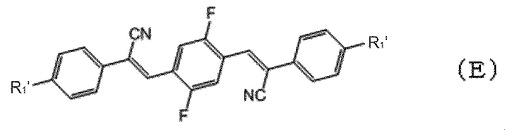

新規化合物および該化合物を含む有機半導体材料

【課題】キャリア移動度と安定性が高く、有機半導体材料として好適な新規化合物を提供する。

【解決手段】

下記一般式(E)で表される化合物。

【化1】

(但し、R1'は、炭素数1〜3のフッ素置換アルキル基である。)

当該化合物はキャリア移動度と安定性が高く、容易な製造プロセスで成膜が可能であるため、有機半導体材料として好適である。特に有機薄膜トランジスタ用の有機半導体層として好適に使用することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜上にチャネル保護膜として機能する絶縁層が設けられたボトムゲート構造のトランジスタを有する半導体装置において、酸化物半導体膜上に接して設けられる絶縁層、及び/または、ソース電極層及びドレイン電極層の形成後に不純物除去処理を行うことで、エッチングガスに含まれる元素が、酸化物半導体膜表面に不純物として残存することを防止する。酸化物半導体膜の表面における不純物濃度は、5×1018atoms/cm3以下、好ましくは1×1018atoms/cm3以下とする。

(もっと読む)

半導体装置

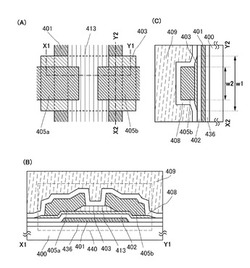

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、シリコンを含む絶縁膜と、絶縁膜上の酸化物半導体膜と、酸化物半導体膜上のシリコンを含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有する構造とし、少なくともゲート電極と重畳する酸化物半導体膜は、絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%より低い領域を有し、当該領域以外の酸化物半導体膜のシリコン濃度は、当該領域より小さくなる構造とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

薄膜トランジスタ回路基板、及びその製造方法

【課題】厚いゲート絶縁層を有する薄膜トランジスタと、薄いゲート絶縁層を有する薄膜トランジスタとを備えた回路基板を提供する。

【解決手段】ポリシリコン半導体層の上下に、ボトムゲート型薄膜トランジスタのゲート絶縁層とトップゲート型薄膜トランジスタのゲート絶縁膜とを各々設け、トップゲート型薄膜トランジスタのゲート絶縁膜の厚さをボトムゲート型薄膜トランジスタのゲート絶縁層の厚さと異ならせる。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】Inと、M1と、M2と、Znと、を含む酸化物材料であり、M1=13族元素、代表的にはGaであり、M2の元素は、M1の元素よりも含有量が少ない材料を提供する。M2としてはTi、Zr、Hf、Ge、Snなどが挙げられる。M2を含ませることで、酸化物半導体材料における酸素欠損の発生を抑制することができる。酸素欠損がほとんど存在しないトランジスタを実現できれば、半導体装置の信頼性を向上させることができる。

(もっと読む)

液晶表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供することを課題の一とする。

【解決手段】画素は、トランジスタと、走査線として機能することができる第1の配線と、信号線として機能することができる第2の配線と、画素電極とを有し、画素は、当該第1の配線と同時に形成された容量線を有さない液晶表示装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程により、ソース電極層及びドレイン電極層を形成後、酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の不純物を除去する工程を行う。

(もっと読む)

半導体装置および電子機器

【課題】低コストかつ簡易なプロセスで保護膜を形成することが可能な半導体装置を提供する。

【解決手段】半導体装置(TFT,バックプレーン等)は、ゲート電極と、ゲート絶縁膜を介してゲート電極と対向配置されると共に、有機半導体を含む半導体層と、半導体層の一部に電気的に接続され、ソースまたはドレインとして機能するソース・ドレイン電極と、半導体層上に設けられ、有機溶媒に可溶であると共に有機半導体と相分離する有機絶縁材料を含む保護膜とを備える。保護膜は、製造プロセスにおいて、有機溶媒に溶かされた状態(溶液の状態)で半導体層上に塗布(または印刷)されることにより形成される。有機溶媒によって半導体層の表面側の一部が溶け出すが、この溶けた部分は上記溶液と相分離する。保護膜に有機絶縁材料を用いる場合であっても、有機溶媒による半導体層の侵食の進行が抑制される。

(もっと読む)

薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置

【課題】隣接する開口部の内部へ有機半導体インクを塗布した際に、互いのインクの混合を抑制し、高い品質を備える薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置を提供する。

【解決手段】隔壁1016における開口部1016bを臨む側面部のうち、隣接する開口部1016cの側の側面部1016eは、側面部1016dを含む他の側面部よりも傾斜が相対的に急峻な斜面となっている。隔壁1016における開口部1016cを臨む側面部のうち、隣接する開口部1016bの側の側面部1016fは、側面部1016gを含む他の側面部よりも傾斜が急峻な斜面となっている。開口部1016bと開口部1016cとの各内部に対して、有機半導体インクを塗布した場合、X軸方向に互いに離れる方向に偏った表面プロファイルを有することになる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置

【課題】有機半導体層の形成に際して、不所望の領域への有機半導体層の形成を抑制し、且つ、隣接する開口部間でのインクの混合を抑制することにより、高い品質を備える薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置を提供する。

【解決手段】隔壁1016には、3つの開口部1016a,1016b,1016cが開けられている。開口部1016b,1016cの各底部には、ソース電極1014a,1014b、ドレイン電極1014c,1014dが露出し、各々がチャネル部として機能する部分である。開口部1016bを臨む側面部のうち、側面部1016d,1016eは、側面部1016iに比べ、傾斜が相対的に急峻な斜面である。開口部1016cを臨む側面部のうち、側面部1016fは、側面部1016jに比べ、傾斜が相対的に急峻な斜面である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

液晶表示装置、表示モジュール及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】酸化物半導体の分野は近年注目されはじめた分野である。そのため、酸化物半導

体層を用いたトランジスタの電気特性と、酸化物半導体層の物性値と、の相関関係が未だ

明らかになっていない。よって、酸化物半導体層の物性値を調整することによって、トラ

ンジスタの電気特性を向上させることを第1の課題とする。

【解決手段】少なくとも、ゲート電極と、酸化物半導体層と、前記ゲート電極と前記酸化

物半導体層との間に挟まれたゲート絶縁層と、を有し、前記酸化物半導体層は、比誘電率

が13以上(又は14以上)である半導体装置を提供する。

(もっと読む)

21 - 40 / 5,376

[ Back to top ]