Fターム[5F110EE08]の内容

Fターム[5F110EE08]の下位に属するFターム

Fターム[5F110EE08]に分類される特許

201 - 220 / 1,684

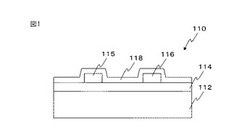

半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。また、本発明の目的は、基材がポリマー材料を有する半導体積層体を提供することである。

【解決手段】半導体積層体(110)を製造する本発明の方法は、(a)基材上にシリコン粒子分散体膜を形成する工程、(b)シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び(c)未焼結半導体シリコン膜に光を照射して、半導体シリコン膜を形成する工程を含む。また、本発明の半導体積層体(110)は、基材(112)及び半導体シリコン膜(118)を有し、基材が、ポリマー材料を有し、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】スパッタ法でトランジスタ、ダイオード等の半導体用途に好適な材料を提供する。具体的には結晶性の高い酸化物半導体膜を形成する作製プロセスを提供する。

【解決手段】意図的に窒素を酸化物半導体に対して添加することにより、六方晶であり、ウルツ鉱型結晶構造を有する酸化物半導体膜を形成する。酸化物半導体膜において、窒素を含む領域の結晶性は、窒素をあまり含まない領域、或いは窒素を意図的に添加していない領域に比べて高くなる。この結晶性の高いウルツ鉱型結晶構造を有する酸化物半導体膜をトランジスタのチャネル形成領域として用いる。

(もっと読む)

高分子化合物、これを含む薄膜及びインク組成物

【課題】高い電荷の移動度が得られる高分子化合物を提供すること。

【解決手段】式(1)及び(2)で表される繰り返し単位からなる群より選ばれる少なくとも1種の繰り返し単位を有する高分子化合物。

[式(1)におけるX11及びX12並びに式(2)におけるX21及びX22は、酸素又はカルコゲン原子を示す。]

(もっと読む)

低分子半導体

【課題】高い移動度および良好な膜形成性を示す半導体化合物を提供する。

【解決手段】下式の低分子半導体。

〔R1、R2は、アルケニル、アルキニル、アリール、アルコキシ、アルキルチオ等〕

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜をチャネルに用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】加熱処理により第1の結晶構造となりうる酸化物半導体膜と、加熱処理により第2の結晶構造となりうる酸化物半導体膜を積層して形成し、その後加熱処理を行うことによって、第2の結晶構造を有する酸化物半導体膜を種として第1の結晶構造を有する酸化物半導体膜へ結晶成長する。このようにして形成した酸化物半導体膜を、トランジスタの活性層に用いる。

(もっと読む)

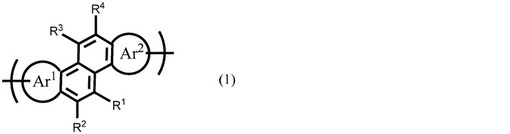

高分子化合物、これを含む薄膜及びインク組成物

【課題】高い電荷の移動度が得られる高分子化合物を提供すること。

【解決手段】式(1)で表される繰り返し単位を有する高分子化合物。

[Ar1及びAr2は、芳香族炭化水素環、複素環、又は芳香族炭化水素環と複素環との縮合環である。R1、R2、R3及びR4は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、アリールオキシ基、アリールチオ基、アリールアルキル基、アリールアルコキシ基、アリールアルキルチオ基、置換シリル基、非置換若しくは置換のカルボキシル基、1価の複素環基、シアノ基又はフッ素原子を示す。]

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

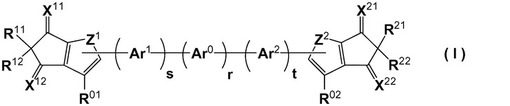

共役系化合物、並びにこれを用いた有機薄膜及び有機薄膜素子

【課題】電子輸送性に優れたn型半導体として利用可能であり、しかも溶剤への溶解性にも優れる共役系化合物の提供。

【解決手段】式(I)で表される共役系化合物。[式中、R01及びR02はアルカン骨格を含む1価の基。R11、R12、R21及びR22は水素原子、ハロゲン原子又は1価の基。X11、X12、X21及びX22は=O,=S又は=CA2(Aは水素原子、ハロゲン原子又は1価の基を示すが、その少なくとも1つは電子吸引性の基。)を示す。Z1及びZ2は−O−,−S−,−Se−,−Te−,−SO−等のいずれかの基を示す。Ar0、Ar1及びAr2は芳香族炭化水素基又は複素環基を示す。rは1〜6の整数、s及びtは0〜6の整数を示す。] (もっと読む)

(もっと読む)

半導体装置

【課題】光感度を向上させた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、柔軟性を有し、可視光に対して透明な透明基板12と、透明基板上に設けられる透明電極14と、透明電極の透明基板と接している面の反対側の一部に設けられる有機半導体層16と、有機半導体層の透明電極と接している面の反対側の表面の上方に設けられる反射層71とを備える。

(もっと読む)

帯電体並びにそれを用いた電界効果トランジスタ及びメモリ素子

【課題】 フローティングゲートメモリやMNOSメモリのような極薄膜の絶縁層を必要とせず、印刷、塗布でメモリ素子が製造可能となる簡便で、注入電荷量の制御が容易な帯電体、並びにこの帯電体をゲート絶縁膜に用いてFETを作製することにより、閾値電圧制御が可能で、長時間制御された閾値電圧状態を保持可能なFET及びメモリ素子を提供する。

【解決手段】 電荷注入が生じる電界強度(以降、電荷注入耐圧)および絶縁耐圧がそれぞれECI,HおよびEBHである絶縁体(以下,高電荷注入耐圧材料)と、その電荷注入耐圧ECI,LがECI,L < ECl,Hの関係にある絶縁体(以下、低電荷注入耐圧材料)の二種類の絶縁体を積層した絶縁物で、高電荷注入耐圧材料と低電荷注入耐圧材料のそれぞれに接し離れた2枚の電極にECI,L < |E| < EBH の電界強度で電圧を印加して低電荷注入耐圧材料側から電荷を絶縁体内に注入して帯電させる帯電体。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能な新規化合物及び新規重合体の提供。

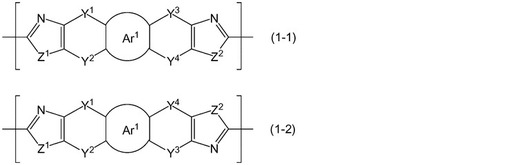

【解決手段】式(1−1)及び式(1−2)で表される構造単位からなる群より選択される、含窒素縮合環化合物。

[式中、Ar1は、芳香環を示し、Y1及びY2のうちいずれか一方は、−C(=X1)−で表される基を示し、他方は、単結合を示し、Y3及びY4のうちいずれか一方は、−C(=X2)−で表される基を示し、他方は、単結合を示し、X1及びX2は、酸素原子等を示し、Z1及びZ2は、酸素原子等を示す。]

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

薄膜トランジスタのための誘電性組成物

【課題】電子機器(例えば、薄膜トランジスタ)は、基板と、誘電性組成物から作られた誘電層とを備える電子機器を提供する。

【解決手段】誘電性組成物は、誘電性材料と、架橋剤と、熱酸発生剤とを含む。特定の実施形態では、誘電性材料は、低k誘電性材料と、高k誘電性材料とを含む。堆積したら、低k誘電性材料と高k誘電性材料とは、別個の相を形成する。熱酸発生剤は、比較的低い温度および/または短い時間で誘電層を硬化させることができ、これにより、これ以外の方法では、誘電層を硬化させることによって変形するであろう低コスト基板材料を選択することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のゲートラスト法の問題点を解決し、さらなる微細化に対応できるゲート構造を実現する。

【解決手段】半導体領域101上から、ダミーゲート構造を除去してリセス107aを形成した後、リセス107aの底部の半導体領域101の表面上に界面層108を形成する。次に、界面層108上及びリセス107aの側壁上に高誘電率絶縁膜109を形成すした後、リセス107a内部の高誘電率絶縁膜109上に、ゲート電極の少なくとも一部となる金属含有膜110を形成する。界面層108上に形成されている部分の高誘電率絶縁膜109の厚さは、リセス107aの側壁上に形成されている部分の高誘電率絶縁膜109の厚さよりも厚い。

(もっと読む)

グラフェン電子素子

【課題】グラフェン電子素子を提供する。

【解決手段】ゲート電極、ゲート電極上に配置されたゲート酸化物、ゲート酸化物上のグラフェンチャネル層、グラフェンチャネル層の両端にそれぞれ配置されたソース電極及びドレイン電極を備えるグラフェン電子素子。グラフェンチャネル層には、複数のナノホールがグラフェンチャネル層の幅方向に一つの列で形成される。更にグラフェンチャネル層には、複数のナノホールがグラフェンチャネル層の長手方向に実質的に直交して配置される。

(もっと読む)

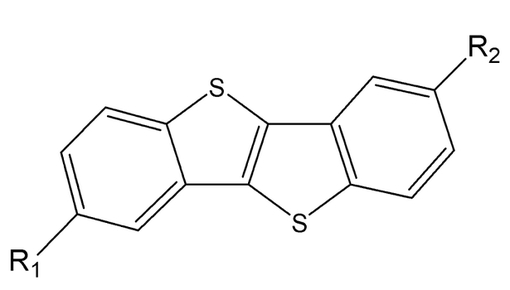

置換カルコゲノアセン化合物及び該化合物を含有する有機半導体デバイス

【課題】有機半導体デバイスに用いることのできる置換カルコゲノアセン化合物を提供するとともに、該化合物を用いた、キャリア電界効果移動度が十分な有機半導体デバイスを提供する。

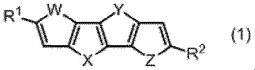

【解決手段】式(1)で表される置換カルコゲノアセン化合物。

(式中、

W、X、Y及びZは、酸素原子、硫黄原子、セレン原子又はテルル原子を表す。

R1及びR2は、炭素数1〜30のフッ素原子を有していてもよいアルキル基、炭素数1〜30のフッ素原子を有していてもよいアルコキシ基、炭素数1〜30のフッ素原子を有していてもよいアルキルチオ基、炭素数2〜30のフッ素原子を有していてもよいアルキニル基、炭素数7〜36のフッ素原子を有していてもよいアリール基又は炭素数5〜34のフッ素原子を有していてもよいヘテロアリール基を表す。)

(もっと読む)

高分子化合物、化合物およびその用途

【課題】光電変換素子に含まれる有機層に用いた場合に、光電変換素子の光電変換効率が高くなる高分子化合物を提供することを目的とする。

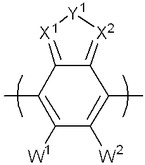

【解決手段】式(1)で表される構造単位を有する高分子化合物。

(1)

〔式中、X1及びX2は、同一又は相異なり、窒素原子又は=CH−を表す。Y1は、硫黄原子、酸素原子、セレン原子、−N(R1)−又は−CR2=CR3−を表す。R1、R2及びR3は、同一又は相異なり、水素原子又は置換基を表す。W1は、シアノ基、フッ素原子を有する1価の有機基又はハロゲン原子を表す。W2は、シアノ基、フッ素原子を有する1価の有機基、ハロゲン原子又は水素原子を表す。〕

(もっと読む)

エッジエミッティングレーザのモノリシックアレイ

【課題】相分離誘電体構造を備える電子デバイスの製造方法を提供する。

【解決手段】本製造方法は、半導体層を堆積し、低誘電率材料、高誘電率材料及び液体を含む誘電体組成物を低誘電率材料及び高誘電率材料を相分離させずに液相堆積し、低誘電率材料および高誘電率材料の相分離を生成することを含む。低誘電率材料は半導体層に最も近い誘電体構造の領域内の高誘電率材料の濃度に比べて高濃度であり、半導体層の堆積は、誘電体組成物を液相堆積する前、または相分離を生成した後になされる。

(もっと読む)

201 - 220 / 1,684

[ Back to top ]