Fターム[5F110EE08]の内容

Fターム[5F110EE08]の下位に属するFターム

Fターム[5F110EE08]に分類される特許

161 - 180 / 1,684

二価結合を有する小分子チオフェン化合物を備える装置

【課題】溶液処理可能であり及び/又は周囲環境条件でよい安定性を示す小分子チオフェン化合物を備える装置を提供する。

【解決手段】多くの電極と接触している半導体層を備える電子装置であって、前記半導体層は、少なくとも1個の二価結合、及び、複数のチオフェン単位から成る小分子チオフェン化合物を含む。小分子チオフェン化合物は、化合物が、特定数(平均値でない)のチオフェン単位を持ち、少なくとも約90質量%、又は少なくとも約98質量%の純度を有する。

(もっと読む)

同時両極性電界効果型トランジスタ及びその製造方法

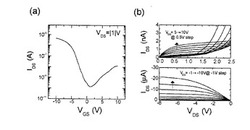

【課題】単一金属酸化物半導体材料をチャネル層として使用時に極性をp型伝導又はn型伝導に変更できる同時両極性電界効果型トランジスタを実現し、さらに、該同時両極性TFTを用いたCMOS構造のトランジスタを提供する。

【解決手段】基板上に設けたチャネル層と、前記チャネル層上又は下にゲート絶縁膜を介して設けられて前記チャネル層のキャリア濃度を制御するゲート電極を有する電界効果型トランジスタにおいて、前記チャネル層材料は、酸化第一スズ(SnO)薄膜であり、前記チャネル層とゲート絶縁膜との界面の欠陥準位密度が5×1014cm−2eV−1以下であり、前記チャネル層は、電子(n型)及び正孔(p型)伝導性の両方の動作が可能な同時両極性を有することを特徴とする同時両極性電界効果型トランジスタ。

(もっと読む)

ジチオケトピロロピロール系ポリマー

【課題】高いフィールド効果移動性、空気安定性、及び良好な溶解性を示す半導体ポリマーを提供すること。

【解決手段】ピロロ[3,4−C]ピロールー2,5−ジチオンを必須単位とし、該化合物の3−位及び6−位を結合手として繰り返し単位を構成し、エテニル、エチニル、アリール、置換アリール、ヘテロアリール、置換ヘテロアリール等を共重合成分として含むポリマー。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子

【課題】有機半導体に対する接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】金属層24Aと、金属層24Aの表面の少なくとも一部に付着したカーボンナノチューブ24Bと、を有する有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

有機半導体としてのアザペリレン類

【課題】有機半導体材料として使用できるアザペリレン化合物の提供。

【解決手段】下記一般式(I)で表されるアザペリレン化合物。

(式中、R1、R2、R3及びR4のそれぞれは、独立して、H、非置換又は置換されているアルキル、非置換又は置換されているアルケニル、非置換又は置換されているアルキニル、非置換又は置換されているアリール、ハロゲン、Si(RH)3、XR6から選択されるか、R1とR2、R2とR3、R3とR4の一つ以上が、それらが結合する炭素原子と一緒になって、飽和又は不飽和の、非置換又は置換されている炭素環又は複素環を形成する。)

(もっと読む)

半導体メモリ装置

【課題】高度に集積化したDRAMを提供する。

【解決手段】基板201上にメモリセルアレイを駆動するための回路202を形成し、その上にビット線205を形成し、ビット線205上に半導体領域208とワード線210a、210b、キャパシタを形成する。ビット線が半導体領域208の下に位置し、ワード線210a、210b、キャパシタが半導体領域208の上に位置するため、ビット線205の配置の自由度が高まり、オープンビット線型のDRAMとすることで6F2以下、あるいはセルトランジスタの構造を特殊なものとすることで4F2以下とできる。

(もっと読む)

多環縮環化合物、多環縮環重合体及びこれらを含む有機薄膜

【課題】高い電荷輸送性を発揮し得る構造を有するとともに、溶媒への溶解性にも優れる多環縮環重合体を提供すること。

【解決手段】式(1)で表される構造単位を有する多環縮環重合体。 (もっと読む)

(もっと読む)

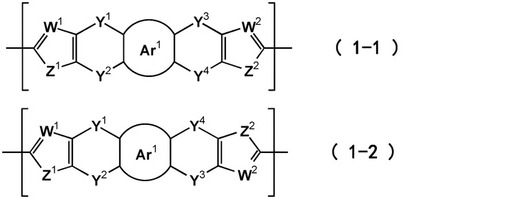

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能であり、有機溶媒への溶解性にも優れる含窒素縮合環化合物を提供すること。

【解決手段】式(1−1)又は式(1−2)で表される構造単位を有する含窒素縮合環化合物。 (もっと読む)

(もっと読む)

電子装置およびその製造方法

【課題】グラフェンシートを使い、大電流をオンオフできる電子装置を提供する。

【解決手段】電子装置は基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部では前記グラフェンシートから4個以上の炭素原子が除去されており、前記各々の開口部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む少なくとも5個の炭素原子からなるジグザグ形状の端部により画成されている。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

有機電子デバイス用組成物、有機電子デバイスの作製方法、有機電子デバイス及び電界効果トランジスタ

【課題】 電荷輸送性や移動度が高く、安定性に優れた有機半導体層、及びOn/Off比が高い有機電子デバイスを得ること。また、この有機電子デバイスを低コストに製造すること。

【解決手段】 特定構造の有機半導体材料と特定の有機化合物とを含有する有機電子デバイス用組成物を用いる。具体的には、アヌレン構造を有する有機化合物、及び芳香環基とアルキル基がエステル結合、カルボン酸アミド結合、カルボニル結合又はフェニルエステル結合している有機化合物を含有することを特徴とする有機電子デバイス用組成物を用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置

【課題】酸化物半導体膜を用いたトランジスタに安定した電気特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】n型酸化物半導体膜中にp型酸化物半導体材料を含ませることで酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。これは、n型酸化物半導体膜中の意図せずに生じた電子が、p型酸化物半導体材料中に生じたホールと再結合することにより、消滅するためである。従って、酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。

(もっと読む)

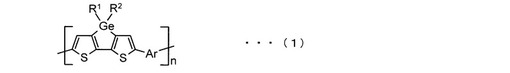

ジチエノゲルモール重合体及びそれを含有した有機半導体デバイス

【課題】耐久性及び半導体特性の安定性に優れた有機半導体材料として有用である熱安定性の高いジチエノゲルモール重合体、及びそれを含有する有機半導体材料より形成される有機半導体デバイスを提供する。

【解決手段】ジチエノゲルモール重合体は、下記化学式(1)

【化1】

(式中、R1及びR2はそれぞれ独立して置換基を有してもよい炭素数1〜20の炭化水素基であり、Arは置換基を有してもよい2価の芳香環と、芳香環数2〜7の置換基を有してもよい2価の多核芳香環と、置換基を有してもよい2価の芳香環及び/又は芳香環数2〜7の置換基を有してもよい2価の多核芳香環を複数連結させた2価のアリーレン基とから選ばれる何れかであり、nは少なくとも2の正数)で示されるものである。有機半導体デバイスは、このジチエノゲルモール重合体を有機半導体層とするものである。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

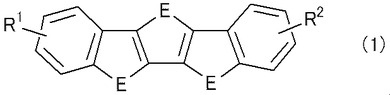

置換ベンゾカルコゲノアセン化合物

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

【解決手段】式(1)

(式中、Eはそれぞれ独立に、硫黄またはセレン原子を表す。

R1及びR2は、それぞれ独立に、水素原子、分岐状のアルキル基を有するアリール基、又は、分岐状のアルキル基を有するヘテロアリール基を表す。前記の分岐状のアルキル基を有するアリール基の合計炭素数は9〜30であり、前記の分岐状のアルキル基を有するアリール基は、置換基を有していてもよい。前記の分岐状のアルキル基を有するヘテロアリール基の合計炭素数は7〜30であり、前記の分岐状のアルキル基を有するヘテロアリール基は、置換基を有していてもよい。

R1及びR2の少なくとも一方は、前記の分岐状のアルキル基を有するアリール基、又は、前記の分岐状のアルキル基を有するヘテロアリール基である。)

で表される置換ベンゾカルコゲノアセン化合物。

(もっと読む)

161 - 180 / 1,684

[ Back to top ]