Fターム[5F110EE08]の内容

Fターム[5F110EE08]の下位に属するFターム

Fターム[5F110EE08]に分類される特許

101 - 120 / 1,684

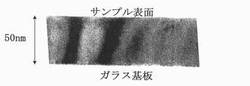

酸化物半導体薄膜層を有する積層構造及び薄膜トランジスタ

【課題】酸化物薄膜の結晶配置の方向を制御し、良質な酸化物薄膜を提供する。

【解決手段】酸化物層と絶縁層からなる積層構造であって、前記酸化物層のキャリア濃度が1018/cm3以下、平均結晶粒径が1μm以上であり、前記酸化物層の結晶が、前記絶縁層の表面に柱状に配置していることを特徴とする積層構造。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】新規な非シリコン系半導体薄膜を用いた薄膜トランジスタを提供する。

【解決手段】ガリウムが酸化インジウムに固溶していて、原子比Ga/(Ga+In)が0.001〜0.12であり、全金属原子に対するインジウムとガリウムの含有率が80原子%以上であり、In2O3のビックスバイト構造を有する酸化物薄膜を用いることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子

【課題】大きい仕事関数および高い電気伝導度を有する電極を具備した電子素子を提供する。

【解決手段】0.1S/cm以上の電気伝導度を有する導電性物質および低表面エネルギー物質を含み、第1面と、前記第1面に対向する第2面と、を有し、前記第2面の低表面エネルギー物質の濃度が、前記第1面の低表面エネルギー物質の濃度より高く、前記第2面の仕事関数が5.0eV以上であり、かつ前記第2面の電気伝導度が1S/cm以上である大きい仕事関数および高い電気伝導度を有する電極、を具備した電子素子である。

(もっと読む)

有機薄膜トランジスタ及び有機薄膜トランジスタの製造方法

【課題】有機半導体層の形成位置について、別途精密な制御を必要とすることなく、高精細なパターニングが行われた有機半導体層を有する有機薄膜トランジスタ及びその製造方法を提供することにある。

【解決手段】ソース電極1、ドレイン電極2、ゲート電極3、有機半導体層4及びゲート絶縁膜5を備え前記ソース電極1及び前記ドレイン電極2の表面エネルギーが、いずれも30mN/m以下であることを特徴とする。

(もっと読む)

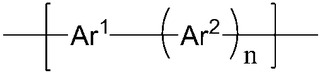

高分子化合物及びそれを用いた有機半導体素子

【課題】高いキャリア移動度を有する高分子化合物を提供すること。

【解決手段】式(1)で表される構造単位を有する高分子化合物であって、

(1)

〔式中、Ar1は、置換基を有していてもよいアリーレン基又は置換基を有していてもよいヘテロアリーレン基を表す。Ar2は、置換基を有していてもよいアリーレン基又は置換基を有していてもよいヘテロアリーレン基を表す。nは、0〜3の整数を表す。Ar2が複数個ある場合、それらは同一であっても相異なってもよい。〕2個の高分子化合物の主鎖間のキャリア伝導性と高分子化合物の主鎖内のキャリア伝導性の両方が大きく、高いキャリア移動度を有する高分子化合物。

(もっと読む)

半導体装置の作製方法

【課題】チャネル形成領域が形成される半導体層のチャネル形成領域と逆側近傍の加工方法を工夫した半導体装置の作製方法を提供する。

【解決手段】少なくとも結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、少なくとも第1のエッチングと第2のエッチングを行い、第1のエッチングは非晶質半導体膜の一部を残存させつつ行い、第2のエッチングは非晶質半導体膜上の被覆膜を除去させた後に、非晶質半導体膜に対するエッチングレートが高く、且つ結晶性半導体膜に対するエッチングレートが低い条件により行い、積層半導体膜に設けられた結晶性半導体膜の一部を露出させる。

(もっと読む)

薄膜トランジスタ

【課題】高移動度の薄膜トランジスタ、その製造方法及びその製造に用いるスパッタリングターゲットを提供する。

【解決手段】元素In,Ga及びZnを下記領域1、2又は3の原子比の範囲で含む酸化物を活性層とし、電界効果移動度が25cm2/Vs以上である薄膜トランジスタ。

領域1

0.58≦In/(In+Ga+Zn)≦0.68

0.15<Ga/(In+Ga+Zn)≦0.29

領域2

0.45≦In/(In+Ga+Zn)<0.58

0.09≦Ga/(In+Ga+Zn)<0.20

領域3

0.45≦In/(In+Ga+Zn)<0.58

0.20≦Ga/(In+Ga+Zn)≦0.27

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体記憶装置

【課題】電力の供給がない状況でも記憶内容の保持が可能かつ、書き込み回数にも制限がない新たな構造の半導体記憶装置を提供する。

【解決手段】第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方と接続し、第1のトランジスタのゲートが第3のトランジスタのソースまたはドレインの一方、およびキャパシタを構成する一対の容量電極の一方と接続し、第1のトランジスタのソースまたはドレインの他方および第3のトランジスタのソースまたはドレインの他方がビット線と接続し、第3のトランジスタのゲートがワード線と接続し、第2のトランジスタのゲートおよびソースまたはドレインの他方がソース線と接続し、キャパシタを構成する一対の容量電極の他方が共通配線と接続し、共通配線はGNDに接続し、共通配線は上面から見て網状に設けられ、第3のトランジスタはその網の目に設けられる半導体記憶装置。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

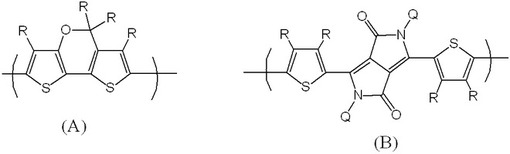

高分子化合物及びそれを用いた有機光電変換素子

【課題】長波長の光の吸光度が大きい高分子化合物を提供する。

【解決手段】式(A)で表される繰り返し単位と式(B)で表される繰り返し単位とを含む高分子化合物。

〔式(A)及び式(B)中、Q及びRは、同一又は相異なり、水素原子、フッ素原子、フッ素化されていてもよいアルキル基、フッ素化されていてもよいアルコキシ基、アリール基、ヘテロアリール基等で表される基を表す。複数個あるQは、同一でも相異なっていてもよい。複数個あるRは、同一でも相異なっていてもよい。〕

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体組成物

【課題】高い電界効果移動度、良好なフィルム形成特性、および複合システムにおける高性能のための適切な形態を示す半導体組成物を提供する。

【解決手段】ボトムゲート型のボトムコンタクト型TFT10は、ゲート電極18およびゲート誘電体層14と接触した基板16を含む。ゲート電極18は、ここでは基板16の頂上に記載されているが、ゲート電極は基板内のくぼみとして位置することもできる。ゲート誘電体層14は、ゲート電極18とソース電極20、ドレイン電極22、および半導体層12とを分離することが重要である。半導体組成物から形成される半導体層12は、ソース電極20とドレイン電極22との間に延びる。この半導体組成物は、ポリマー結合剤および小分子半導体を含む。半導体層中の小分子半導体は、100ナノメートル未満の結晶サイズを有する。組成物から形成されたデバイスは、高い移動度および優れた安定性を示す。

(もっと読む)

グラフェン電子素子及び製造方法

【課題】グラフェン電子素子及び製造方法を提供する。

【解決手段】ゲート電極として作用する導電性基板と、基板上に配置されたゲートオキサイドと、ゲートオキサイド上で互いに離隔された一対の第1金属と、第1金属上で、第1金属の間に延びたグラフェンチャネル層と、グラフェンチャネル層の両端にそれぞれ配置されたソース電極及びドレイン電極と、を備えるグラフェン電子素子である。

(もっと読む)

有機トランジスタの製造方法

【課題】良好な特性を有する有機トランジスタを、インクジェット法により製造する。

【解決手段】有機半導体層7は、インクジェット法によって、有機半導体材料を溶媒に溶解した有機半導体溶液を塗布して形成され、塗布された有機半導体溶液の縁部71が、ソース電極5とドレイン電極6間に配置されるように、ソース電極5とドレイン電極6間のちょうど中間位置よりずらした位置に、塗布領域の中心が位置するように、有機半導体溶液を塗布することを特徴とする。また、ソース電極5が配置されている位置、又はドレイン電極6が配置されている真上に、塗布領域の中心が位置するように、有機半導体溶液を塗布する。

(もっと読む)

101 - 120 / 1,684

[ Back to top ]