Fターム[5F110EE08]の内容

Fターム[5F110EE08]の下位に属するFターム

Fターム[5F110EE08]に分類される特許

21 - 40 / 1,684

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

新規な芳香族重合体

【課題】比較的大きい溶解度等の好ましい特性を有する芳香族重合体を提供する。

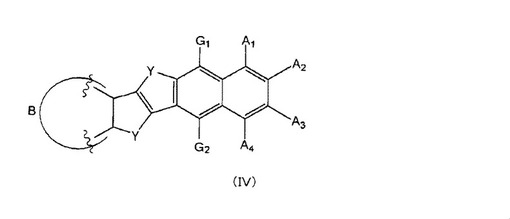

【解決手段】式(IV)で表される縮合多環芳香族部分を2以上有する芳香族重合体:

(G1、G2、A1〜A4は、結合、水素原子、特定の置換基であり、Bは、ベンゼン環部分を有する縮合環であり、Yはカルコゲンである)。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

高分子化合物及びそれを用いた電子素子

【課題】光電変換素子に含まれる有機層に用いた場合に、開放端電圧が大きくなる高分子化合物の提供。

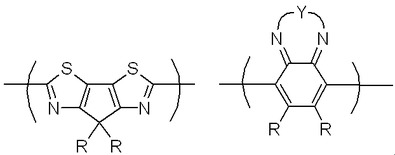

【解決手段】式(I)で表される構成単位、及び、式(II)で表わされる構成単位を有する高分子化合物。

(I)(II)〔式(I)及び式(II)中、Rは、水素原子、ハロゲン原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、アリールオキシ基、アリールチオ基、アリールアルキル基、アリールアルコキシ基、アリールアルキルチオ基、アシル基、アシルオキシ基、アミド基、酸イミド基、イミノ基、アミノ基、置換アミノ基、置換シリル基、置換シリルオキシ基、置換シリルチオ基、置換シリルアミノ基、複素環基、複素環オキシ基、複素環チオ基、アリールアルケニル基、カルボキシル基又はシアノ基を表す。Yは、2価の基を表す。〕

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

化学センサ用薄膜トランジスタ

【解決手段】化学センサは、第1のトランジスタと第2のトランジスタとを備える電子機器である。第1のトランジスタは、第1の半導体とカーボンナノチューブとから作られる半導体を備えている。第2のトランジスタは、第2の半導体から作られる半導体層を備えており、カーボンナノチューブは含んでいない。この2種類のトランジスタは、化学化合物への応答という点で異なっており、その応答の差を利用し、特定の化学化合物の属性を決定することができる。

【効果】この化学センサは、爆発性化合物、例えば、トリニトロトルエン(TNT)の使い捨て可能なセンサとして有用であろう。この電子機器を分析器とともに使用し、分析器は、電子機器によって作られた情報を処理する。

(もっと読む)

有機半導体装置の製造方法

【課題】塗布開始場所以外の場所からの結晶成長を防止し、配向度の高い有機半導体薄膜を形成できるようにする。

【解決手段】有機半導体材料を含むインク11の塗布開始場所からインク11を乾燥させ、インク11中の有機半導体材料を結晶化させて有機半導体薄膜15を形成する。このとき、ノズル部2として、基板12の表面と対向する先端面2fを構成するオーバハング部を有したノズル胴体部2aと、ノズル胴体部2aの先端面2fから基板12側に突出すると共に一方向を長手方向として延設された吐出口2gを有する溶液吐出部2cとを備えたものを用いる。そして、溶液吐出部2cの下端を基板12から離間させた状態でインク11を吐出し、吐出されたインク11にて溶液吐出部2cと基板12の間に液溜まりを形成しつつ、ノズル部2を吐出口2gの長手方向に対する垂直方向に移動させることによりインク11をライン状に塗布する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁性基板に含まれている不純物が半導体層に作用するのを防止して、半導体装置の信頼性を向上させる。

【解決手段】

提供される半導体装置は、絶縁性基板1上に下地絶縁層2を介して半導体層3を形成する半導体装置に係り、下地絶縁層2に不純物として含まれるボロン又はアルミニウムの濃度が、絶縁性基板表面で1×1022原子/cm3以下で、かつ、絶縁性基板表面から100nm以上離れた領域で1×1019原子/cm3以下の条件を満たして、絶縁性基板表面から半導体層3に向かって漸次減少する態様で分布する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

電子装置およびその製造方法

【課題】開口部を形成されることにより、大きなバンドギャップを有するグラフェンシートを有する電子装置を提供する。

【解決手段】基板と、前記基板上に形成されたグラフェンシート23と、前記グラフェンシートの一端に形成されたソース電極23Sと、前記グラフェンシートの他端に形成されたドレイン電極23Dと、前記グラフェンシート上ゲート絶縁膜を介して形成され、前記グラフェンシートにゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部23Aよりなる開口部列と、を備え、前記複数の開口部はいずれも、三つのジグザグ端により画成されて正三角形の形状を有し、前記ジグザグ端のうち二つは、前記ソース電極とドレイン電極を結んだ方向に対し30°の角度をなし、もう一つのジグザグ端は90°の角度をなし、それぞれの正三角形の向きを揃えて形成されている。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

有機薄膜トランジスタ

【課題】電界効果移動度が高く、オフ電流が小さい有機薄膜トランジスタを提供することである。

【解決手段】有機半導体層の内部のうち、ソース電極の真上又は真下に位置する部分を第1の部分とし、ドレイン電極の真上又は真下に位置する部分を第2の部分とし、第1の部分と第2の部分とは異なる部分を第3の部分とした場合に、ドーピング領域が、第3の部分、第1の部分と第3の部分、又は第2の部分と第3の部分に存在する有機薄膜トランジスタである。

(もっと読む)

21 - 40 / 1,684

[ Back to top ]