Fターム[5F110EE22]の内容

Fターム[5F110EE22]の下位に属するFターム

テーパ状 (986)

Fターム[5F110EE22]に分類される特許

161 - 180 / 866

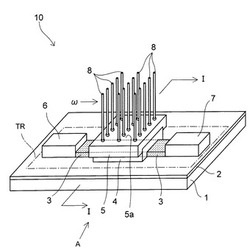

圧力センサとその製造方法

【課題】圧力センサとその製造方法において、従来よりも微小な領域の圧力を測定できるようにすること。

【解決手段】チャンネルとしてグラフェン層3を備えたトランジスタTRと、トランジスタTRのゲート5上に片方の端部が接続された圧電材料を含むナノワイヤ8とを有する圧電センサ10による。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

カーボンナノウォールの選択成長方法、およびカーボンナノウォールを用いた電子デバイス

【課題】カーボンナノウォールの選択成長方法を提供すること。

【解決手段】SiO2 からなる基板100上に、正方形が三角格子状に配列されたパターンのTi膜101を形成した。次に、SiO2 基板100上にカーボンナノウォールを成長させた。そして、Tiからのカーボンナノウォールの成長開始時間よりも長く、SiO2 からのカーボンナノウォールの成長開始時間よりも短い時間で成長を終了させた。ここで、SiO2 からのカーボンナノウォールの成長開始時間は、Tiからの成長開始時間よりも長い。その結果、SiO2 基板100上のうち、Ti膜101が形成されずにSiO2 が露出している領域にはカーボンナノウォールが成長せず、Ti膜101上にのみ、カーボンナノウォール102が形成された。

(もっと読む)

電界効果トランジスタ(FET)およびそれを形成する方法

SeOIの連想メモリでデータを比較するデバイス

【課題】連想メモリの比較デバイス、比較デバイスを制御する方法、および連想メモリを提供する。

【解決手段】データビットを格納する第1のトランジスタT1およびデータビットの補数を格納する第2のトランジスタT2によって形成されたメモリセルであって、各トランジスタは、セミコンダクタ・オン・インシュレータ基板上に作られ、各々は、フロント制御ゲート、およびトランジスタを遮断するように制御するバック制御ゲートBG1、BG2を有する、メモリセルと、各々のフロント制御ゲートに公称読出し電圧を加えることによって読出しモードで動作させ、一方、バック制御ゲートBG1、BG2を、一方をビット(DATA)、他方をビットの補数(DATAb)で制御し、ビット(DATA)と格納されたビットが一致する場合には各々のうちの通過トランジスタを遮断し、各々のソースに連結されたソース線SLの電流の有無を検出する比較回路を備える。

(もっと読む)

半導体装置

【課題】ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を提供する。

【解決手段】ドリフト領域2と、ベース領域3と、ベース領域3を挟んでドリフト領域2に対向して設けられたソース電極12と、ドリフト領域2とベース領域3とにゲート絶縁膜を介して接するトレンチ構造の複数のゲート電極6と、2つのゲート電極6の間において、ドリフト領域2とベース領域3との境界に沿って設けられ、ベース領域3に接する長さがゲート電極6よりも短いトレンチ構造のゲート電極7と、を備え、ソース電極12は2つのゲート電極6の間において、ソース電極12からゲート電極7に向かう方向に設けられたトレンチ9bの中に、ゲート電極7に近接した位置まで延在し、ゲート電極6のソース電極側の端とゲート電極7のソース電極側の端との間において、トレンチ9bの内壁面に露出したベース領域3に接していること。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを有する半導体装置において、より高い耐衝撃性を付与することを目的の一とする。より多様化する用途に対応でき、利便性が向上した信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】半導体装置において、基板上に、ゲート電極層と、ゲート絶縁層と、酸化物半導体層とを含むボトムゲート構造のトランジスタと、トランジスタ上に絶縁層と、絶縁層上に導電層とを有し、絶縁層は酸化物半導体層を覆い、かつゲート絶縁層と接して設けられ、酸化物半導体層のチャネル幅方向において、ゲート電極層上でゲート絶縁層と絶縁層とは端部が一致し、導電層は、酸化物半導体層のチャネル形成領域と、ゲート絶縁層及び絶縁層の端部とを覆い、かつゲート電極層と接して設けられる。

(もっと読む)

Uゲートトランジスタ製造方法

【課題】短チャネル性能を改善した非プレーナ半導体トランジスタ構造及びその製造方法を提供する。

【解決手段】基板360上にある絶縁層301上にU字形フィン305が形成され、その一部の上にゲート誘電体層362及びゲート電極363が形成され、ソース領域403及びドレイン領域404が、U字形フィン305の両側に形成される。ゲート電極363は、ゲート誘電体層362とともに、U字形フィン305の一部の上側表面306及び反対の位置にある2つの側壁307、並びにU字形フィン305の中にある凹部319の一部の底面320及び向かい合って位置する2つの側壁364を覆い、電流を流すチャネル領域の幅を実効的に増やす。U字形トランジスタ構造の電流−電圧特性は、ゲート電圧範囲全体にわたって、デバイスの角部分の性能によって支配され、短チャネル効果が最小限に抑えられ、閾値下の電流及び駆動電流が最適化される。

(もっと読む)

浮遊ボディセル、浮遊ボディセルを含むデバイス、ならびに浮遊ボディセルの形成方法。

バックゲート上に配置される浮遊ボディセルのアレイと、バックゲートから間隔の開いた浮遊ボディセルのソース領域およびドレイン領域と、を含む浮遊ボディセル構造。浮遊ボディセルは、ピラーの間に伸長するチャネル領域を有する大量の半導電性材料を各々含み、ピラーは、U形状トレンチなどの間隙によって分離されうる。アレイの浮遊ボディセルは、別のゲートに電気的に結合され、別のゲートは、大量の半導電性材料の側壁上に配置されてもよいし、大量の半導電性材料の間隙内に配置されてもよい。浮遊ボディセルデバイスを形成する方法も開示される。  (もっと読む)

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

Uゲートトランジスタ製造方法

【課題】MOSトランジスタを小型化する場合に主な制約要因となる短チャネル効果を抑制できるUゲートトランジスタを提供する。

【解決手段】非プレーナ多角トランジスタ構造を製造するための工程が以下のように構成される。フィンの上側表面上にマスクを有する半導体材料のフィンが、第1の絶縁層上に形成される。マスクの上側表面を露出させたまま、フィン上に第2の絶縁層が形成され、フィンと第2の絶縁層との間に保護層が堆積される。次に、マスクが除去され、保護層に隣接するフィン内にスペーサが形成される。フィン内に、底面及び向かい合っている側壁を有する凹部が形成される。フィン305の上側表面及び反対の位置にある側壁上、並びにフィン内の凹部の底面及び向かい合っている側壁上に、ゲート誘電体層362及びゲート電極363が形成される。ゲート電極363の両側においてフィン内にソース領域403及びドレイン領域404が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

多層拡張ドレイン構造を有する高電圧トランジスタを作製する方法

【課題】拡張ドレイン領域を有する高電圧トランジスタを作製する方法を提供する。

【解決手段】拡張ドレイン領域を有する高電圧トランジスタを作製する方法を提供は、第一の導電型である基板上に第一の導電型であるエピタキシャル層を形成し、そして、エピタキシャル層をエッチングして、エピタキシャル層の第一及び第二の側壁部を形成する一対の離間した溝部を形成することを含む。各溝部の一部には、第一及び第二の側壁部をカバーするように、誘電体層が充填される。

そして、溝部の残りの部分に導電材料が充填されて、基板及びエピタキシャル層から絶縁された第一及び第二のフィールドプレート部材が形成される。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

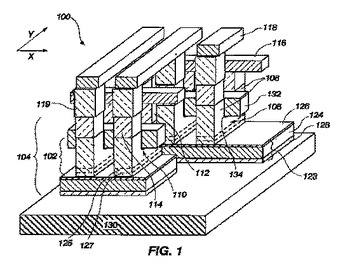

低リークGANMOSFET

エンハンスメント・モードGaN MOSFET(100)が、AlGaN(又はInAlGaN)障壁層(118)上のSiO2/Si3N4ゲート絶縁層(124)を用いて形成される。SiO2/Si3N4ゲート絶縁層(124)のSi3N4部分(120)は、ゲート絶縁層(124)と障壁層(118)との間の接合での界面準位の形成を低減させ、SiO2/Si3N4ゲート絶縁層(124)のSiO2部分(122)は、漏れ電流を著しく低減させる。

(もっと読む)

(もっと読む)

マルチゲートIII−V量子井戸構造

マイクロ電子構造を形成する方法を記載する。方法の実施形態は、基板上にIII−Vトライゲートフィンを形成する段階と、III−Vトライゲートフィンの周囲にクラッド材を形成する段階と、クラッド材の周りに高誘電率ゲート誘電体を形成する段階とを備える。 (もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

発光装置及び電子機器

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥

離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを

可能とすることを目的する。また、様々な基材に被剥離層を貼りつけ、軽量された半導体

装置およびその作製方法を提供することを課題とする。

【解決手段】基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を

設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化

を行い、金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または

金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。

(もっと読む)

非平面ゲルマニウム量子井戸デバイス

非平面(ノンプレーナ)ゲルマニウム量子井戸構造を形成する技術が開示される。量子井戸構造は、IV族又はIII−V族の半導体材料を用いて実現されることができ、ゲルマニウムフィン構造を含む。一例において、非平面量子井戸デバイスが提供され、このデバイスは、基板(例えば、シリコン上にSiGe又はGaAsのバッファを有する)と、IV族又はIII−V族材料のバリア層(例えば、SiGe、GaAs又はAlGaAs)と、ドーピング層(例えば、デルタ/変調ドープされる)と、アンドープのゲルマニウム量子井戸層とを有する量子井戸構造を含む。アンドープのゲルマニウムフィン構造が量子井戸構造内に形成され、該フィン構造上に頂部バリア層が堆積される。ゲートメタルが、フィン構造を横切って堆積される。ドレイン/ソース領域がフィン構造のそれぞれのエンドに形成され得る。  (もっと読む)

(もっと読む)

161 - 180 / 866

[ Back to top ]