Fターム[5F110EE22]の内容

Fターム[5F110EE22]の下位に属するFターム

テーパ状 (986)

Fターム[5F110EE22]に分類される特許

101 - 120 / 866

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

半導体装置、表示装置、電子機器

【課題】作製工程を増やすことなく、凹凸形状の画素電極を作製することを目的とする。

【解決手段】凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成する。こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

半導体装置、発光装置、モジュール、及び電子機器

【課題】電気光学装置において、新規の構成を有する画素回路を用いることにより、従来の構成の画素よりも高い開口率を実現することを目的とする。

【解決手段】i行目を除くゲート信号線の電位は、i行目のゲート信号線106が選択されている以外の期間においては定電位となっていることを利用し、i−1行目のゲート信号線111をi行目のゲート信号線106によって制御されるEL素子103への電流供給線として兼用することで配線数を減らし、高開口率を実現する。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

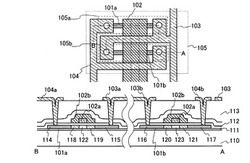

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置の作製方法

【課題】必要十分なキャパシティをもつ保持容量を備えた半導体装置を提供する。

【解決手段】金属表面を有する基板11と、前記金属表面を有する基板上に形成された絶縁膜12と、前記絶縁膜上に形成された画素部とを有する半導体装置において、前記画素部は、TFTと、該TFTと接続する配線21とを有しており、保持容量は、前記金属表面を有する基板、前記絶縁膜および前記配線により構成されている。前記絶縁膜の膜厚が薄いほど、また、前記絶縁膜と前記配線の接する領域の面積が大きいほど、大きなキャパシティを得られるので有利である。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

表示装置

【課題】

表示装置の高解像度化や小型化、さらには画素の開口率の向上を行った場合でも、半導体層に入射する光を効果的に遮断し、ホトコン電流による表示品質の低下を防止することが可能な表示装置を提供すること。

【解決手段】

前記基板上に、第1絶縁膜と、ゲート電極と、ゲート電極の上層に形成された第2絶縁膜と、前記第2絶縁膜の上層に形成された半導体層とが積層され、前記第1絶縁膜は開口部を有し、前記ゲート電極は、前記開口部に倣って形成された窪みを有し、前記半導体層の全部、又は前記半導体層の端部は、平面的に見て前記窪みと重畳していることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

101 - 120 / 866

[ Back to top ]