Fターム[5F110EE22]の内容

Fターム[5F110EE22]の下位に属するFターム

テーパ状 (986)

Fターム[5F110EE22]に分類される特許

21 - 40 / 866

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

薄膜トランジスタおよび電子機器

【課題】性能向上を容易に実現することが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備える。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】製造コストの低減、およびプロセス時間の短縮を可能とするfinFETの製造方法を提供する。

【解決手段】finFETは、ソース領域、ドレイン領域、およびソース領域とドレイン領域との間のチャネル領域を有するフィンを備えるように形成される。上記フィンは、半導体ウエハ上でエッチングされる。ゲートスタックは、上記チャネル領域に直接接触する絶縁層と、上記絶縁層に直接接触する導電性のゲート材料とを有するように形成される。上記ソース領域および上記ドレイン領域は、上記フィンの第一領域を露出するためにエッチングされる。次に、上記第一領域の一部が、ドーパントでドーピングされる。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

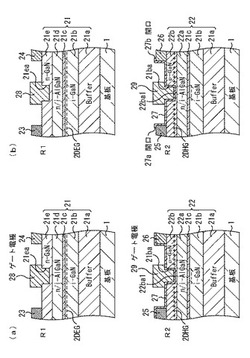

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体装置

【課題】1T−DRAMにおいて、高いGIDL電流は、主にPN接合でのリーク電流によるものであり、データ保持時にリーク電流が発生する原因にもなり、DRAMにおける電荷保持時間を低下させている。

【解決手段】ドレイン拡散層のうちゲート電極とオーバーラップする部分を、不純物濃度の異なる2つの部分に分けている。これら2つの部分のうち、不純物濃度がより低い一方の部分では、ボディ部に隣接しており、電界が低減されるためリーク電流が抑制される。また、不純物濃度がより高い他方の部分では、ボディ部から絶縁されており、ゲート絶縁層との界面において比較的大きなトンネル効果が得られる。その結果、GIDL電流を増大しつつ、PN接合によるリーク電流を抑制し、データ保持時間を増大させることが可能となっている。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

21 - 40 / 866

[ Back to top ]