Fターム[5F110EE22]の内容

Fターム[5F110EE22]の下位に属するFターム

テーパ状 (986)

Fターム[5F110EE22]に分類される特許

41 - 60 / 866

半導体装置

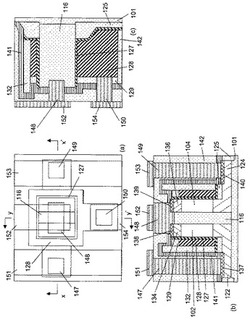

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

電子デバイス

【課題】薄膜トランジスタおよび/または電子デバイスの電荷キャリア移動度を増大させ、高い移動度および優れた安定性を達成する。

【解決手段】薄膜トランジスタの半導体層は、半導体組成物として、ポリマー結合剤および小分子半導体を含む。また、半導体層は、ソース電極およびドレイン電極の間の方向に配列したアライメント層上に堆積されている。アライメント層は、電子デバイスの電界効果移動度を増大させるために使用される。

(もっと読む)

半導体装置およびその製造方法

【課題】電気特性の低下や変動を生じにくい半導体装置とその製造方法を提供する。

【解決手段】ワイドバンドギャップ半導体層を半導体層に用いたトランジスタにおいて、水分・大気成分を透過しにくいパッシベーション性を有する絶縁層でワイドバンドギャップ半導体層を島状に分離する構造とする。該島状のワイドバンドギャップ半導体層の端部がその絶縁層と接する構成となるため、半導体層の端部からワイドバンドギャップ半導体層に水分・大気成分が侵入する現象を防止できる。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置

【課題】動作特性および信頼性の向上した、新規なマルチゲート構造のトランジスタを提

供することを課題とする。

【解決手段】2つ以上のゲート電極と、直列に接続した2つ以上のチャネル形成領域、ソ

ース領域、ドレイン領域、及び高濃度不純物領域を有する半導体層と、を有するマルチゲ

ート構造のトランジスタにおいて、ソース領域側に近接するチャネル形成領域のチャネル

長が、ドレイン領域側に近接するチャネル形成領域のチャネル長よりも大きくする。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

有機薄膜トランジスタアレイ基板及びその製造方法

【課題】有機薄膜トランジスタアレイ及びその製造方法を提供する。

【解決手段】本製造方法は、ベース基板に、第1透明導電薄膜層とソース・ドレイン金属薄膜層を順次形成し、第1回パターニング工程を行って、第1画素電極パターン、ソース電極パターン、ドレイン電極パターン及びデータラインパターンを形成する工程と、有機半導体薄膜層とゲート絶縁薄膜層とを順次形成し、第2回パターニング工程を行って、前記ソース電極パターンとドレイン電極パターン上に位置する有機半導体アイランドパターン及びゲート絶縁アイランドパターンを形成する工程と、一層のパッシベーション層薄膜を形成し、第3回パターニング工程を行って、データラインパッド領域を形成する工程と、第2透明導電薄膜層とゲート金属薄膜層とを順次形成し、第4回パターニング工程を行って、第2画素電極パターン、ゲート電極パターン、及びゲートラインパターンを形成する工程とを備える。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗が小さく高性能なナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、第1方向に延在するナノワイヤ形状のチャネル領域3と、チャネル領域3を間に挟むように離間して設けられかつチャネル領域3よりも幅が広いソース領域およびドレイン領域8,9と、チャネル領域3、ソース領域およびドレイン領域8,9と基板との間に設けられ膜厚が薄い凹形状の領域を有する絶縁膜2と、チャネル領域3上の半導体層の少なくとも側面に設けられたゲート絶縁膜と、前記ゲート絶縁膜に対して前記第1領域上の前記半導体層と反対側に設けられたゲート電極6と、ゲート電極6の、ソース領域およびドレイン領域8,9に対向する側面に設けられた絶縁体のゲート側壁7と、を備え、半導体層は半導体層直下の前記凹形状の領域の部分に延在している。

(もっと読む)

アレイ基板及びその製造方法

【課題】アレイ基板及びその製造方法を提供する。

【解決手段】本発明による製造方法は、基板に無機材料の突起を形成するステップと;それぞれ第一透明導電層と第一金属層からなる反射領域パターン、ゲートライン及びゲートラインから分岐して出されるゲート電極と共通電極を形成するステップと;半導体層からなる活性化ランドパターンと第二金属層からなるデータラインパターンを形成し、活性化ランドパターン上でデータラインに接続されるソース電極とドレイン電極、及び半導体層からなるチャネルを形成するステップと;基板に無機材料を塗布し、無機材料に対して焼き戻し工程を行って一平坦層を形成し、ドレイン電極にビアホールを形成するステップと;反射領域に、ビアホールを介してドレイン電極に接続され且つ第二透明導電層からなる画素電極を形成するステップと、を有する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルとなるナノワイアの周囲をゲート電極が取り巻いて形成されているFETが、より容易に高い精度で製造できるようにする。

【解決手段】被覆ナノワイア103を配置した基板121のゲート電極形成領域の上に、被覆ナノワイア103に交差して下部ゲート電極122に重なる上部ゲート電極124を形成する。上部ゲート電極124の形成は、公知のリソグラフィー技術とリフトオフとにより行えばよい。例えば、被覆ナノワイア103が下部ゲート電極122と交差して配置されている基板121の上に、電子ビーム露光により電極形成部に開口を備えるレジストパターンを形成し、この上に、電極材料を堆積する。この後、先に形成してあるレジストパターンを除去すれば、上部ゲート電極124が形成できる。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出

来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有

する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われ

る回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる

電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置と

する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

41 - 60 / 866

[ Back to top ]