Fターム[5F110EE32]の内容

薄膜トランジスタ (412,022) | ゲート (57,237) | サイドウォールを有するもの (2,180) | 堆積によるもの (1,135)

Fターム[5F110EE32]に分類される特許

141 - 160 / 1,135

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバICの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジスタを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

半導体基板の作製方法

【課題】SOI基板等の単結晶半導体層を有する半導体基板において、該単結晶半導体層を厚膜化することを課題の一とする。また、半導体基板の量産性を向上させることを課題の一とする。

【解決手段】単結晶半導体基板上に非晶質半導体層を形成した後、絶縁層を介して支持基板と貼り合わせ、該単結晶半導体基板の一部を、非晶質半導体層とともに支持基板上に転載する。そして、非晶質半導体層を固相エピタキシャル成長させることで、支持基板上に厚い単結晶半導体層を形成するものである。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変化しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体基板の作製方法

【課題】加速した水素イオンの照射量を増やすことなく、低い加熱処理温度で単結晶半導体基板からベース基板に半導体層を転載できるSOI基板の作製方法を提供することを課題の一とする。

【解決手段】劈開に寄与することなく、脆化領域から半導体基板の表面側に拡散する水素に着眼した。そして、脆化領域からの水素の拡散を防ぎ、且つ脆化領域と半導体基板の表面に挟まれた領域に水素を供給できるキャップ膜を半導体基板に形成し、当該半導体基板からベース基板に半導体層を転載する発明に至った。特に、半導体基板に形成するキャップ膜の水素濃度は水素イオンの照射量以上とすればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板に形成され、SOI基板を構成する半導体層の素子領域の周囲が素子分離により囲まれた半導体装置において、素子分離に起因する信頼度の低下を防ぐことのできる技術を提供する。

【解決手段】トレンチ分離を構成するディープトレンチ4の上部のトレンチ幅を、1.2μmよりも狭くすることにより、ディープトレンチ4の内部を絶縁膜5で埋め込んだ際に生じる中空7が、絶縁膜5の上面に現れるのを防ぐことができる。ディープトレンチ4の上部のトレンチ幅が狭くなることにより懸念される互いに隣接する素子領域間の耐圧の低下は、ディープトレンチ4の上部に、ディープトレンチ4の内部に埋め込まれた絶縁膜5と繋がるLOCOS絶縁膜6を形成することによって回避する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】メタルゲートを用いたCMISまたはCMOS構造の集積回路デバイスにおいて、Nチャネル領域およびPチャネル領域におけるゲート絶縁膜、メタルゲート層等のつくり分けに関しては、種々の方法が提案されているが、プロセスが複雑になる等の問題があった。

【解決手段】本願発明は、CMOS集積回路デバイスの製造方法において、Nチャネル領域およびPチャネル領域において、ゲート電極膜形成前の高誘電率ゲート絶縁膜の電気的特性を調整するためのチタン系窒化物膜を下方のチタンを比較的多く含む膜と、上方の窒素を比較的多く含む膜を含む構成とするものである。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】トランジスタが有するしきい値相当分の電圧/電流のロスを低減し、プロセスの簡略化、及び回路構成の簡素化を目的とした整流特性を有する半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子に整流回路を設ける。整流回路において、電波を受信するアンテナと整流回路のトランジスタのゲートとドレイン端子との間に、コイルを重ねて配置することで、電波を受信するアンテナとコイルの結合を利用して、ダイオード単体と比較しダイオードとコイルが出力する電圧を大きくし、整流効率を向上させる。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層のテーパー形状を有する端部の特性を良好にすることを課題とする。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、単結晶半導体基板とベース基板とを、絶縁膜を介して貼り合わせ、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁膜を介して第1の単結晶半導体層を形成し、第1の単結晶半導体層に対してドライエッチングを行って、端部の形状がテーパー形状である第2の単結晶半導体層を形成し、第2の単結晶半導体層の端部に対して、ベース基板側の電位を接地電位としたエッチングを行う。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセルと、ソース線及びビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線と電気的に接続された第4の駆動回路と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

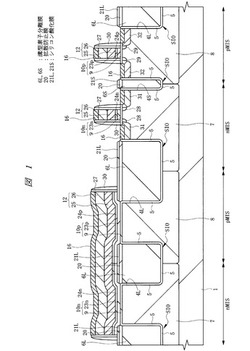

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

141 - 160 / 1,135

[ Back to top ]