Fターム[5F110EE32]の内容

薄膜トランジスタ (412,022) | ゲート (57,237) | サイドウォールを有するもの (2,180) | 堆積によるもの (1,135)

Fターム[5F110EE32]に分類される特許

81 - 100 / 1,135

半導体装置

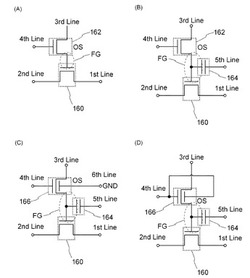

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の側壁側にサイドウォールを精度よく形成することが可能な半導体装置の製造方法及び半導体装置を提供することを目的とする。

【解決手段】まず、SOI基板5の一方面側においてゲート電極34上及びゲート電極34の周囲の領域に第1絶縁膜40を形成する。次に、第1絶縁膜40上に積層させる構成で第1絶縁膜40とは材質の異なる第2絶縁膜42を形成する。そして、第1絶縁膜40及び第2絶縁膜42におけるゲート電極34の側壁34a側の部分を残しつつ、第2絶縁膜42よりも第1絶縁膜40のほうが、エッチング速度が遅くなるように第1絶縁膜40及び第2絶縁膜42を除去し、ゲート電極34の側壁34a側にサイドウォール45を形成する。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

酸化物材料および半導体装置

【課題】トランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、このような半導体装置を実現する酸化物材料を提供する。

【解決手段】それぞれ、c軸配向し、ab面、上面または被形成面に垂直な方向から見て少なくとも三角形状または六角形状の原子配列を有し、c軸においては、金属原子が層状または金属原子と酸素原子とが層状に配列しており、In2SnZn2O7(ZnO)m(mは0または自然数。)で表される、ab面(または上面または被形成面)においては、a軸またはb軸の向きが異なる二種以上の結晶部分を含む酸化物膜を用いる。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】素子面積の増大を抑制しつつ、駆動電流の高いON/OFF比と安定した特性を実現できる半導体装置及びその製造方法を提供する。

【解決手段】絶縁層と、絶縁層上に形成された半導体層と、半導体層に形成された部分空乏型のトランジスター10とを備え、トランジスター10は、半導体層上に絶縁膜を介して形成されたゲート電極14と、ゲート電極14両側下の半導体層に形成されたソース15又はドレイン16と、ボディーの下部に設けられた不純物層17,18とを有し、不純物層17,18は、ボディー領域の下部の両側端部に形成され、ソース15、ドレイン16とは接しない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極及び空孔付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に選択的に一対の第1の半導体層6が設けられ、第1の半導体層6にそれぞれ1側面を接し、空孔5上に一対の第2の半導体層8が設けられ、第2の半導体層8間に2側面を接し、残りの周囲にゲート絶縁膜14を介してゲート電極15に包囲された、歪み構造の第3の半導体層7が設けられ、第1及び第2の半導体層(6、8)には概略ソースドレイン領域(10、11、12、13)が設けられ、第3の半導体層7には概略チャネル領域が設けられ、ソースドレイン領域(10、13)及び包囲型ゲート電極15には配線体(19、20、22、23)が接続されているMISFET。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を介して対向する一対の第2の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられるゲート絶縁膜と、ゲート絶縁膜上に設けられて、かつ第1の領域に重畳する第1の電極と、を有し、第1の領域は、c軸配向した結晶部を有する非単結晶の酸化物半導体領域であり、一対の第2の領域は、ドーパントを含んで、かつ複数の結晶部を有する酸化物半導体領域であることを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高性能でかつばらつきの少ないナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に第1絶縁膜を形成する工程と、第1絶縁膜上に設けられ、第1領域と第1領域よりも幅の広い第2および第3領域とを有しこれらの第2および第3領域の少なくとも一方が第1領域に接続するように構成された第1半導体層と、第1半導体層の上面に設けられるマスクと、を形成する工程と、マスクを用いて、前記第1半導体層の第1領域の側面にイオン注入を行う第1イオン注入を行う工程と、イオン注入を行った後に、第1熱処理を行う工程と、マスクを除去した後、第1半導体層の前記第1領域の少なくとも側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲート電極の、第2および第3領域側の側面に絶縁体のゲート側壁を形成する工程と、少なくとも第1半導体層の第2および第3領域に第2イオン注入を行う工程と、とを備えている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

81 - 100 / 1,135

[ Back to top ]