Fターム[5F110EE32]の内容

薄膜トランジスタ (412,022) | ゲート (57,237) | サイドウォールを有するもの (2,180) | 堆積によるもの (1,135)

Fターム[5F110EE32]に分類される特許

41 - 60 / 1,135

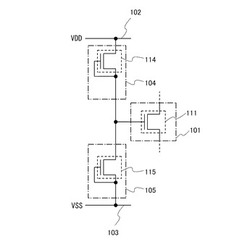

駆動回路、当該駆動回路の作製方法および当該駆動回路を用いた表示装置

【課題】作製中にESDにより半導体素子が破壊されることを抑制する駆動回路および当該駆動回路の作製方法を提供する。また、リーク電流の小さい保護回路が設けられた駆動回路および当該駆動回路の作製方法を提供する。

【解決手段】駆動回路中の半導体素子と電気的に接続して、駆動回路中に保護回路を設け、駆動回路中の半導体素子となるトランジスタと駆動回路中の保護回路を形成するトランジスタを同時に形成することにより、駆動回路の作製中にESDにより半導体素子が破壊されることを抑制する。さらに、駆動回路中の保護回路を形成するトランジスタに酸化物半導体膜を用いることにより、保護回路のリーク電流を低減する。

(もっと読む)

酸化物半導体膜の成膜方法、半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して信頼性が劣る場合があった。そこで、信頼性が高い酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】酸化物半導体膜に含まれる水素、窒素および炭素などの不純物は酸化物半導体膜の半導体特性を低下させる要因となる。例えば、酸化物半導体膜に含まれる水素および窒素は、酸化物半導体膜を用いたトランジスタのしきい値電圧をマイナス方向へシフトさせてしまう要因となる。また、酸化物半導体膜に含まれる窒素、炭素および希ガスは、酸化物半導体膜中に結晶領域が生成されることを阻害する。そこで、酸化物半導体膜の不純物濃度を低減することで、高い信頼性を有するトランジスタを作製する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供する。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層を除去するエッチング処理と、硝酸、硝酸によって酸化された半導体基板を構成する半導体材料を溶解する物質、半導体材料の酸化速度及び酸化された半導体材料の溶解速度を制御する物質、及び亜硝酸を含み、亜硝酸の濃度が10mg/l以上1000mg/l以下である混合液を用いて、未損傷の半導体領域に対して損傷半導体領域を選択的に除去するエッチング処理と、を行うことで半導体基板を再生する。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】消費電力の増大を抑制し且つ微細化を達成した半導体装置および当該半導体装置の作製方法を提供する。また、安定した電気的特性が付与された、信頼性の高い半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜に電界で加速されたイオンを照射して、当該酸化物半導体膜の表面の平均面粗さを低減することにより、トランジスタのリーク電流の増大および消費電力の増大を抑制することができる。さらに、加熱処理を行って、酸化物半導体膜が当該酸化物半導体膜表面に垂直なc軸を有する結晶を含むように形成することにより、酸化物半導体膜の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜上に金属元素を含む絶縁膜を形成し、注入法により該金属元素を含む絶縁膜を通過して導入されたドーパントを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置

【課題】プロセス技術が比較的簡単、且つ、少ない素子数で多値情報を記憶することがでるメモリを提供する。

【解決手段】メモリ素子426において、第1の記憶素子における第1の電極417の形状の一部を、第2の記憶素子における第1の電極417の形状と異ならせることで、第1の電極417と第2の電極420の間の電気抵抗が変化する電圧値を異ならせて、1ビットを越える多値の情報の記憶を一つのメモリセルで行う。第1の電極417を部分的に加工することで単位面積当たりの記憶容量を増大することができる。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

41 - 60 / 1,135

[ Back to top ]