Fターム[5F110FF28]の内容

Fターム[5F110FF28]に分類される特許

141 - 160 / 3,049

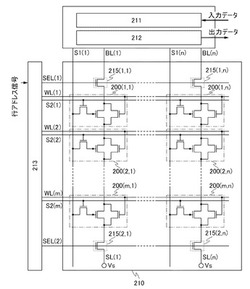

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

半導体装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複

数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを

課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる

酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャ

ネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成する

ことにより、開口率を上げる。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

液晶表示装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

【課題】絶縁層上の有機半導体層をレーザ光を用いてパターニングしたときであっても、有機半導体層に損傷が生じ難い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(A)基体10上にゲート電極12を形成した後、(B)基体10及びゲート電極12上にゲート絶縁層13を形成し、次いで、(C)基体10に到達する分離溝16をゲート絶縁層13に形成した後、(D)ゲート絶縁層13上及び分離溝16の底部に露出した基体10上に有機半導体層14を形成し、次に、(E)少なくとも分離溝16の底部に露出した基体10上に形成された有機半導体層14の部分にレーザ光を照射して分離溝16の底部の少なくとも一部を露出させる一方、有機半導体層14の上に一対のソース/ドレイン電極15を形成する各工程から成る。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、20cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート絶縁膜15と、In(a)Ga(b)Zn(c)O(d)(a>0,b>0,c>0,a+b+c=1,d>0)で表され、a≦37/60、b≦91a/74−17/40、b≧3a/7−3/14、c≦3/5を満たす第1の領域A1及びIn(p)Ga(q)Zn(r)O(s)(q/(p+q)>0.250,p>0,q>0,r>0,s>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層と、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

表示装置

【課題】動作速度を向上させる。

【解決手段】第1のソース及び第1のドレインの一方に画像信号線を介して画像信号が入力され、第1のゲートに第1の走査信号線を介して第1の走査信号が入力される第1のトランジスタ101と、2つの電極のうちの一方の電極が第1のトランジスタの第1のソース及び第1のドレインの他方に電気的に接続される容量素子102と、第2のソース及び第2のドレインの一方が第1のトランジスタ101の第1のソース及び第1のドレインの他方に電気的に接続され、第2のゲートに第2の走査信号線を介して第2の走査信号が入力される第2のトランジスタ103と、第1の電極が第2のトランジスタの第2のソース及び第2のドレインの他方に電気的に接続される液晶素子104と、を備え、画像信号線としての機能を有する導電層及び第2の走査信号が入力される走査信号線としての機能を有する導電層は、互いに離間し、且つ並置されている。

(もっと読む)

半導体装置

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1

の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するよ

うに、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるよう

に第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形

成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導

体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2

の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

薄膜デバイス及びその製造方法

【課題】酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上のインジウムを含む酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分の表面層15におけるXPSスペクトルのインジウム3d軌道起因のピーク位置が、表面層15の下部に存在する酸化物半導体領域におけるXPSスペクトルのインジウム3d軌道起因のピーク位置よりも、高エネルギ側にシフトしている。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、30cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート電極と接するゲート絶縁膜15と、In(x)Zn(1−x)O(y)(0.4≦x≦0.5,y>0)で表される第1の領域A1及びIn(a)Ga(b)Zn(c)O(d)(b/(a+b)>0.250,c>0,d>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層12と、互いに離間して配置されており、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】インジウム、チタン、及び亜鉛を含む酸化物半導体層をチャネル形成領域とするトランジスタ、及び該トランジスタを含む半導体装置を提供する。酸化物半導体層に接するバッファ層としては、チタン、アルミニウム、ガリウム、ジルコニウム、ハフニウム、又は希土類元素から選択された一以上の元素の酸化物を含む金属酸化層を適用することができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】少なくともゲート電極層、ゲート絶縁膜、及び半導体層が順に積層されたボトムゲート型のトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】加熱処理により酸素を放出する絶縁体基板と、該絶縁体基板上に設けられた酸化物半導体膜と、を有し、該酸化物半導体膜にチャネルが形成されるトランジスタを有する半導体装置である。加熱処理により酸素を放出する絶縁体基板は、絶縁体基板の少なくとも酸化物半導体膜が設けられる側に、酸素イオン注入を行うことで作製することができる。

(もっと読む)

半導体装置の作製方法

【課題】薄膜トランジスタのしきい値電圧を制御するため、薄膜トランジスタのチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設けた際に、プロセス数の増加を招くことなく、電気特性の優れた薄膜トランジスタを備えた半導体装置を得る。

【解決手段】酸化物半導体層131の上方に設ける第2のゲート電極133を形成するとき、酸化物半導体層131のパターニングと同時に形成することで、第2のゲート電極133の作製に要するプロセス数の増加を削減する。

(もっと読む)

141 - 160 / 3,049

[ Back to top ]