Fターム[5F110GG51]の内容

Fターム[5F110GG51]の下位に属するFターム

Fターム[5F110GG51]に分類される特許

121 - 140 / 359

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

(式中、Y1〜Y4はそれぞれ独立に、酸素原子、硫黄原子、またはメチレン基を表し、l、mおよびnはそれぞれ独立に0または1を表し、rおよびsはそれぞれ独立に1または2を表す)

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

電界効果型トランジスタ及び電界効果型トランジスタの製造方法

【課題】非晶質酸化物を含む活性層を有する電界効果型トランジスタ及び電界効果型トランジスタの製造方法において、活性層への水分や酸素の影響が抑制されると共に閾値シフトの改善された電界効果型トランジスタ及び電界効果型トランジスタの製造方法を提供する。

【解決手段】電界効果型トランジスタ10において、非晶質無機材料からなる保護層24を、活性層18の少なくともソース電極20Aとドレイン電極20Bとの電極間に対応する領域を覆うように配置し、且つ該保護層24のバンドギャップが活性層18のバンドギャップより大きい保護層24とする。

(もっと読む)

半導体装置及びその製造方法

基板(11)上に形成されたフィン型半導体領域(13)の両側部にエクステンション領域(17)が設けられている。フィン型半導体領域(13)を跨ぐと共にエクステンション領域(17)と隣り合うようにゲート電極(15)が形成されている。ゲート電極(15)と隣り合う領域のフィン型半導体領域(13)の上部に、エクステンション領域(17)よりも高い抵抗率を有する抵抗領域(37)が形成されている。 (もっと読む)

半導体装置

【課題】動作性能および信頼性の高い半導体装置の提供を課題とする。

【解決手段】シリコン基板上に設けられた酸化シリコン膜と、単結晶シリコン基板の一部よりなりTFTの活性層となる単結晶の島状シリコン層となる前の単結晶シリコン基板を熱酸化して得られ、酸化シリコン膜に貼り合わせ界面にて貼り合わせて設けられた膜厚が0.05μm〜0.5μmの酸化シリコン膜と、活性層を熱酸化して設けられた他の面の酸化シリコン膜と、により取り囲まれた活性層と、活性層上に設けられたゲート電極と、を有し、単結晶の島状シリコン層は、膜厚が0.05μm〜0.5μmの酸化シリコン膜を介して水素が導入された単結晶シリコン基板を水素が導入された部分で分断して得られたものである半導体装置を提供する。

(もっと読む)

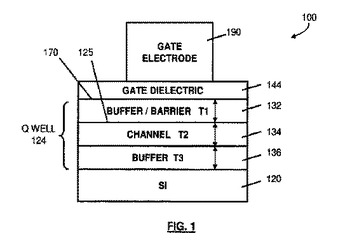

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

表示装置用基板とその製造方法、表示装置、レーザアニーリング装置、結晶化半導体膜の製造方法

【課題】工程数の増加を伴うことなく、結晶の異方性が異なる複数の領域を有する結晶化半導体膜を形成することができる結晶化半導体膜の製造方法を提供する。

【解決手段】レーザビーム6を走査している最中に、レーザビーム6の単位時間当たりの照射量を複数の領域3・4・5に応じた照射量に連続して変えることにより、結晶の異方性の異なる複数の領域3・4・5からなる結晶化半導体膜を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】薄膜トランジスタを有する半導体装置において、薄膜トランジスタの半導体層を、金属元素が添加された酸化物半導体層とする。金属元素として鉄、ニッケル、コバルト、銅、金、モリブデン、タングステン、ニオブ、及びタンタルの少なくとも一種類以上の金属元素を用いる。また、酸化物半導体層はインジウム、ガリウム、及び亜鉛を含む。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を拡大させることなく、メモリセルにおける単位面積あたりの容量値を増やした半導体記憶装置を実現する。

【解決手段】メモリセル100は、トランジスタ101と、メモリ素子104と、第1の容量102と、第2の容量103と、を有する。第1の容量102は、トランジスタ101を構成する半導体膜108、ゲート絶縁膜114およびゲート電極109で構成され、トランジスタ101と同時に形成される。第2の容量103は、メモリ素子104を構成する電極107ならびに電極107上に形成した絶縁膜113および電極111から構成される。また、第2の容量103は、第1の容量102の直上に形成する。このように、メモリ素子104と並列に接続する、第1の容量102および第2の容量103を形成する。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】スイッチ部またはバッファ部と、論理回路部と、画素部と、を有する表示装置において、画素部は、第1の逆スタガ型薄膜トランジスタと、第1の逆スタガ型薄膜トランジスタの配線に接続する画素電極と、を有し、スイッチ部またはバッファ部は、第1の絶縁層、半導体層、及び第2の絶縁層を挟む第1のゲート電極及び第2のゲート電極を有する第2の逆スタガ型薄膜トランジスタを有し、論理回路部は、第3の逆スタガ型薄膜トランジスタ及び第4の逆スタガ型薄膜トランジスタにより構成されるインバータ回路を有し、第1の逆スタガ型薄膜トランジスタ乃至第4の逆スタガ型薄膜トランジスタは、同じ極性とする。インバータ回路はEDMOS回路である。

(もっと読む)

薄膜電界効果型トランジスタおよびそれを用いた電界発光装置

【課題】本発明の目的は、移動度が高く、高ON/OFF比を示す薄膜電界効果型トランジスタおよびそれを用いて高階調な電界発光装置を提供することである。

【解決手段】基板上に、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を有する薄膜電界効果型トランジスタであって、前記活性層が、室温から温度の低下と伴に電子キャリア濃度が減少する傾向を有し、その活性化エネルギーが0.04eV以上0.10eV以下である非晶質酸化物を含有することを特徴とする薄膜電界効果型トランジスタ、およびそれを用いた電界発光装置。

(もっと読む)

半導体装置及びその作製方法

【課題】メモリ回路の高集積化、あるいは小型化を果たす上で、メモリセルの面積を縮小することが重要になると考えられる。特別なプロセスを増やすことなくメモリセルの面積を縮小化した記憶装置を提供することを課題とする。

【解決手段】選択トランジスタと、メモリ素子と、アシスト容量とを有する半導体装置であって、メモリ素子の一方の電極とアシスト容量の一方の電極は共通電極であり、アシスト容量の他方の電極は不純物を有する半導体膜から形成され、メモリ素子の一方の電極とアシスト容量の他方の電極は絶縁膜を介して重畳している。

(もっと読む)

半導体装置の作製方法

【課題】 電気光学装置の製造コストを低減する技術を提供する。

【解決手段】 電気光学装置を形成するTFTの作製方法において、必要とするパターニング回数を極力低減することにより、製造コストの低減を図る。具体的には、ゲート配線をマスクとして活性層に不純物元素を添加した後、該ゲート配線の線幅をパターニング工程を施すことなく狭め、再度不純物元素を添加する。これによりパターニング回数を増やすことなくLDD領域を形成できる。

(もっと読む)

基板全域にわたって高められた均一性を有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

洗練された半導体デバイスにおいては、異なる結晶方位に対して異方性エッチング挙動を有し得るウエット化学的エッチングプロセスに基いてキャビティを形成することによって、チャネル領域の近くに歪誘起半導体合金を位置させることができる。1つの実施形態では、異方性エッチング挙動に加えて二酸化シリコンに関する高いエッチング選択性を呈するTMAHを用いることができ、それにより、チャネル領域からのオフセットを更に減少させる可能性を追加的に提供する一方で、全体的なプロセスばらつきの大きな原因となることのない極めて薄いエッチング停止層が可能になる。

(もっと読む)

薄膜電界効果型トランジスタおよびそれを用いた表示装置

【課題】本発明の目的は、移動度が高く、高ON/OFF比を示す薄膜電界効果型トランジスタおよびそれを用いた表示装置を提供することである。

【解決手段】基板1上に、少なくとも、ゲート電極2、ゲート絶縁膜3、活性層4−1、ソース電極5−1及びドレイン電極5−2を有する薄膜電界効果型トランジスタであって、前記活性層4−1と前記ソース電極5−1及び前記ドレイン電極5−2の少なくとも一方との間に抵抗層4−2を有し、前記活性層がIn,Zn及びGaより成る群から選ばれる少なくとも1種を含む酸化物を含有し、前記抵抗層が少なくともGaを含有する酸化物を含有し、前記抵抗層の酸化物のGa含有率が前記活性層の酸化物のGa含有率より高いことを特徴とする薄膜電界効果型トランジスタ。

(もっと読む)

薄膜電界効果型トランジスタ

【課題】本発明の目的は、活性層にアモルファス酸化物半導体を用いたTFTであって、駆動耐久性及び駆動安定性に優れたTFTを提供することである。

【解決手段】基板上に、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を有するTFTであって、

1)前記活性層がアモルファス酸化物半導体層であり、該アモルファス酸化物半導体の金属成分中のIn原子比率が70%以上であり、Ga原子比率が25%以下、Al原子比率が25%以下であり、

2)前記ゲート絶縁膜と前記活性層との間に第1界面層を有し、該第1界面層はアモルファス酸化物半導体層であり、該アモルファス酸化物半導体の金属成分中のGa原子比率が5%以上、又はAl原子比率が5%以上であり、

3)前記第1界面層のアモルファス酸化物半導体のGa及びAl原子比率が前記活性層のアモルファス酸化物半導体のGa及びAl原子比率より高い。

(もっと読む)

薄膜電界効果型トランジスタ及びその製造方法

【課題】本発明の目的は、アモルファス酸化物半導体を用いた薄膜電界効果型トランジスタの高精細化が容易で生産性にすぐれた製造方法を提供することにある。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記ゲート電極上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたアモルファス酸化物半導体層と、前記アモルファス酸化物半導体層上にソース電極及びドレイン電極を有する薄膜電界効果型トランジスタの製造方法であって、前記ソース電極及びドレイン電極が電気化学的に酸化され得る金属より形成され、該金属の前記ソース電極とドレイン電極との間にあってチャネル部を形成する領域を電気化学反応により金属酸化物に変質させ、該金属酸化物をエッチングにより除去することにより前記ソース電極及びドレイン電極をパターニングするパターニング工程を有する薄膜トランジスタの製造方法。

(もっと読む)

薄膜電界効果型トランジスタおよびそれを用いた表示装置

【課題】本発明の目的は、移動度が高く、高ON/OFF比を示す薄膜電界効果型トランジスタおよびそれを用いた表示装置を提供することである。

【解決手段】基板1上に、少なくとも、ゲート電極2、ゲート絶縁膜3、活性層4、ソース電極5−1及びドレイン電極5−2を有する薄膜電界効果型トランジスタであって、前記活性層が酸化物半導体層であり、前記活性層と前記ソース電極及びドレイン電極の少なくとも一方との間に酸化物半導体層からなる抵抗層6を有し、前記活性層の電気伝導度が10−4Scm−1以上102Scm−1未満であり、且つ、前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率(活性層の電気伝導度/抵抗層の電気伝導度)が、101以上1010以下であり、前記ソース電極及びドレイン電極の少なくとも一方の前記抵抗層と接する面側がTi又はTi合金層8−1,8−2である薄膜電界効果型トランジスタ。

(もっと読む)

薄膜電界効果型トランジスタおよびそれを用いた表示装置

【課題】本発明の目的は、移動度が高く、高ON/OFF比を示す薄膜電界効果型トランジスタおよびそれを用いた表示装置を提供することである。

【解決手段】基板上に、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を有する薄膜電界効果型トランジスタであって、前記活性層が酸化物半導体層であり、前記活性層と前記ソース電極及び前記ドレイン電極の少なくとも一方との間に前記活性層より電気伝導度の低い抵抗層を有し、前記活性層と前記抵抗層との間に前記活性層の酸化物半導体よりも酸素との結合力の強い元素種を含む酸化物を含有する中間層を有する薄膜電界効果型トランジスタ。

(もっと読む)

SOI基板の作製方法

【課題】他の基板と区別して識別できるマークが形成され、ガラス基板上に、バッファ層を間に介在して単結晶半導体層が設けられたSOI基板を歩留まり良く作製する。

【解決手段】ガラス基板上に、バッファ層を間に介在させて、単結晶半導体層を形成し、バッファ層および単結晶半導体層が積層された積層体の周辺領域を除去してガラス基板を露出させる。そして、バッファ層および単結晶半導体層が積層された積層体の外側に露出するガラス基板にマークを形成する。

(もっと読む)

121 - 140 / 359

[ Back to top ]