Fターム[5F110GG51]の内容

Fターム[5F110GG51]の下位に属するFターム

Fターム[5F110GG51]に分類される特許

101 - 120 / 359

半導体装置の製造方法

【課題】ナノ物質の半導体の性質を利用した半導体装置においては、金属性ナノ物質により半導体装置の半導体特性が劣化する。

【解決手段】半導体装置の製造方法は、はじめに、複数のナノ物質に含まれる半導体性ナノ物質と金属性ナノ物質のうち、半導体性ナノ物質の導電性を低下させる。次に、金属性ナノ物質に、金属性ナノ物質を切断する作用を促進する切断促進物質を付着させる。次に、切断促進物質が付着した金属性ナノ物質を切断する。

(もっと読む)

第3A族インク、並びにその製造方法および使用方法

【課題】基体上への第3a族金属の堆積を容易にするように設計され、ヒドラジン爆発の危険性を回避できる新たな第3a族インク配合物、その製造方法及び第3a族インクを使用して第3a族物質を、VLSI技術におけるシリコンデバイスの金属化、半導体III−V合金の成長、薄膜トランジスタ(TFT)、発光ダイオード(LED)および赤外線検出器などの様々な半導体用途に使用するための基体上に堆積する方法を提供する。

【解決手段】ポリアミン溶媒、第3a族物質/有機物錯体、および還元剤を初期成分として含み、還元剤のモル濃度が第3a族物質/有機物錯体のモル濃度を超えており、第3a族インクは安定な分散物であり、かつ第3a族インクはヒドラジンおよびヒドラジニウムを含まない、第3a族インク。

(もっと読む)

半導体装置の製造方法

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置の製造方法、を提供する。

【解決手段】半導体装置の製造方法は、50nmを超え150nm以下の厚みを有し、第1の層7mと第2の層7nとを有する半導体膜7を形成する工程を備える。半導体膜7を形成する工程時、第1の層7mに含まれる水素の割合は、第2の層7nに含まれる水素の割合よりも小さい。半導体装置の製造方法は、半導体膜7を熱処理することによって、半導体膜7に含まれる水素を低減する工程と、ゲート絶縁膜17およびゲート電極21を形成する工程と、半導体膜7にソース領域9およびドレイン領域13を形成する工程と、半導体膜7を水素雰囲気中で熱処理することによって、半導体膜7に含まれる水素を0.5原子%以上10原子%以下に設定する工程とを備える。

(もっと読む)

差動増幅回路と半導体装置並びに表示装置

【課題】

工程を複雑にすることなく、多結晶シリコン膜に回路特性に適したnチャネル型TFT

とpチャネル型TFTを形成することができる薄膜半導体装置及び差動増幅回路及び表示装置の提供。

【解決手段】

入力対に与えられた信号電圧を差動で受ける差動対(101、102)と、前記差動対の出力対と第1の電源間に接続される負荷素子対(103、104)と、前記差動対と第2の電源間に接続され、前記差動対に定電流を供給する電流源(106)と、を有する差動段(23)を備えた差動増幅回路において、前記差動対、及び/又は、前記負荷素子対は、相対的に低閾値のトランジスタよりなり、前記差動段の電流パスに挿入され、前記電流パスの導通・遮断を制御するスイッチ機能として、前記低閾値のトランジスタよりも高い閾値を有し、制御端子に入力される制御信号によってオン・オフ制御される少なくとも1つのトランジスタ(503)を備える。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】水によるTFT特性の不安定性を改善し、且つTFTの初期特性を向上させる。

【解決手段】基板上に形成されたゲート電極と、前記ゲート電極を覆うように形成されたゲート絶縁層と、前記ゲート絶縁層上に形成された酸化物半導体からなる活性層と、前記活性層と前記ゲート絶縁層の間に又は前記活性層上に、互いに離間して形成されたソース電極及びドレイン電極と、前記ソース電極と前記ドレイン電極で覆われていない前記活性層の上面を覆う疎水性を有する有機単分子膜と、前記活性層上の前記有機単分子膜上に形成された保護層と、を有した薄膜トランジスタを採用する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

半導体素子の作製方法

【課題】 本発明は、非破壊かつ簡便に、所望の電気特性を得るために最適なキャリア濃

度にドーピングできるドーピング装置、並びにドーピング方法、それを用いる薄膜トラン

ジスタの作製方法を提供することを課題とする。

【解決手段】 本発明では、接触角を用いて、半導体素子の電気特性(トランジスタにお

けるしきい値電圧など)を正確かつ精密にモニタし、ドーピング方法を制御することによ

って、特性を制御する。また、本発明により、in−situで特性をモニタすることを

よって、情報を時々刻々取得し、時間遅延なくフィードバックできる。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的とする。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

半導体装置

【課題】半導体装置の表示領域と駆動回路に設けられたTFTの構造を機能に応じて適切なものとするとき、pチャネル型TFTにおいて、チャネル形成領域と、不純物領域との接合に欠陥が形成され、オフ電流が増加することを防止する。

【解決手段】表示領域に第1のnチャネル型TFTが配置され、駆動回路に第2のnチャネル型TFT及びpチャネル型TFTが配置された半導体装置であって、pチャネル型TFTはチャネル形成領域と、これに隣接した不純物領域を有し、不純物領域にはnチャネル型TFTのために添加された不純物元素を含ませない。そのために、pチャネル型TFTのチャネル長はnチャネル型TFTのチャネル長より短くなる。

(もっと読む)

半導体装置及びその製造方法、並びに液晶表示装置

【課題】光センサーと遮光膜を有する半導体装置において、段切れや膜剥がれに起因にする歩留まりの低下を防止することができるとともに、暗電流の増大を防止して光センサーの性能の低下を防止することができる半導体装置及びその製造方法、並びに液晶表示装置を提供することを目的とする。

【解決手段】フォトダイオード15を構成するポリシリコン膜を形成する部分Bの非晶質シリコン膜30の厚みW1が、遮光膜28の周縁に対応した部分Aの非晶質シリコン膜30の厚みW2より薄くなるように、非晶質シリコン膜30を薄膜化する。そして、非晶質シリコン膜30にレーザー光を走査して、非晶質シリコン膜30を多結晶化させてポリシリコン膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】高開口率な表示装置を提供する。

【解決手段】薄膜トランジスタと、保持容量とが設けられた画素と、走査線と、走査線に直交して設けられた信号線と、を有し、走査線の上方には、薄膜トランジスタのソース領域、ドレイン領域、及びチャネル形成領域が形成される部分と保持容量の下部電極となる部分とを有する半導体膜が設けられ、半導体膜上には絶縁膜が設けられ、半導体膜のチャネル形成領域となる部分の上方には、絶縁膜を介して走査線と電気的に接続されたゲート電極が設けられ、半導体膜の下部電極となる部分の上方には、絶縁膜を介して保持容量の上部電極が設けられ、半導体膜は、基板に平行であり、ゲート電極は、保持容量の上部電極より半導体膜を基準に高い場所に設けられ、ゲート電極及び上部電極の上方には、信号線が設けられている表示装置。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体膜に混入する不純物濃度を制御した活性層を有する半導体回路を備えた半

導体装置を提供するものである。

【解決手段】上記目的を解決するため、ガラス基板上に200nm〜500nmの膜厚の

第1の窒化珪素膜と、前記第1の窒化珪素膜上に第2の窒化珪素膜と、前記第2の窒化珪

素膜上にチャネル形成領域となる領域を含む非晶質半導体膜と、を有する構成において、

前記第1の絶縁膜と前記第2の絶縁膜との界面において、ボロンを有する。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

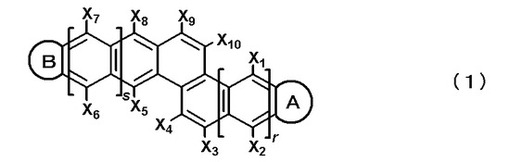

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

[式中、X1〜X10はそれぞれ独立に、水素原子、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、あるいは置換または未置換のアリール基を表し、さらに、隣接するX1〜X10は、互いに結合して置換している炭素原子と共に置換または未置換のベンゼン環を形成していてもよく、Y1およびY2はそれぞれ独立に、酸素原子あるいは硫黄原子を表す]

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

(式中、X1〜X10はそれぞれ独立に、水素原子、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、直鎖、分岐または環状のアルコキシアルキル基、あるいは置換または未置換のアリール基を表し、環Aおよび環Bはそれぞれ独立に置換または未置換のインドール環を表し、rおよびsはそれぞれ独立に、0または1を表し、rおよびsが同時に0を表さない場合、X4とX5は互いに結合して置換している炭素原子と共に置換または未置換のベンゼン環を形成していてもよい)

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層にテトラアセナフト[1,2−a:1’,2’−c:1”,2”−h:1”’,2”’−j]アントラセン誘導体を少なくとも1種含有してなる有機トランジスタ。

(もっと読む)

液晶表示パネル及びその製造方法

【課題】スイッチング素子としてのトップゲート式TFTと、前記TFTを遮光するため

の遮光膜とが設けられた液晶表示パネルにおいて、遮光膜の材料としてMoを採用し、遮

光膜の被覆絶縁層にドライエッチング処理を施してMoの表面を露出させる場合にも、オ

ーバーエッチングによる遮光膜の消失を防げるようにした液晶表示パネルを提供すること

。

【解決手段】本発明の液晶表示パネル1は、遮光膜11がMoからなり、かつ、遮光膜1

1と上層金属配線との電気的接続が、バッファ絶縁膜12とゲート絶縁膜14を貫通する

第1コンタクトホール27を経て遮光膜11と電気的に接続されていると共に層間絶縁膜

16に被覆された第1導電部材25と、層間絶縁膜16を貫通する第2コンタクトホール

28を経て層間絶縁膜16の表面の金属配線と電気的に接続された第2導電部材26と、

を経て行われている。

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層に下式で表される化合物を含有してなる有機トランジスタ。

(X1〜X8は、水素原子、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、あるいはアリール基を表し、R0およびR00は、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、あるいはアリール基で置換されていてもよいナフチル基、アントラセニル基、フェナントレニル基、あるいはベンゾ[b]チエニル基を表し、nは0または1を表す)

(もっと読む)

101 - 120 / 359

[ Back to top ]