Fターム[5F110GG55]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | 製法 (16,298) | 不純物の導入方法 (1,524) | 拡散 (206) | 気相拡散(雰囲気中) (120)

Fターム[5F110GG55]に分類される特許

1 - 20 / 120

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程により、ソース電極層及びドレイン電極層を形成後、酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の不純物を除去する工程を行う。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜上にチャネル保護膜として機能する絶縁層が設けられたボトムゲート構造のトランジスタを有する半導体装置において、酸化物半導体膜上に接して設けられる絶縁層、及び/または、ソース電極層及びドレイン電極層の形成後に不純物除去処理を行うことで、エッチングガスに含まれる元素が、酸化物半導体膜表面に不純物として残存することを防止する。酸化物半導体膜の表面における不純物濃度は、5×1018atoms/cm3以下、好ましくは1×1018atoms/cm3以下とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気的特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】チャネル形成領域、及びチャネル形成領域を挟む低抵抗領域を含む酸化物半導体膜、ゲート絶縁膜、及び上面及び側面を覆う酸化アルミニウム膜を含む絶縁膜が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び酸化アルミニウム膜を含む絶縁膜の上面及び側面の一部に接して設けられる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置

【課題】電流駆動能力がより小さなクロック信号生成回路を適用することが可能な半導体装置を提供する。

【解決手段】nチャネル型トランジスタで構成されるスイッチ及び論理回路を有し、スイッチは導通状態又は非導通状態がクロック信号によって選択され、論理回路は、ブートストラップ回路と、入力信号が入力される入力端子と、反転入力端子と、出力端子とを有し、高電源線と出力端子との接続を反転入力端子に入力される信号によって制御し、低電源線と出力端子との接続を入力端子に入力される信号によって制御することによって、入力信号がローレベル電位の場合には、ブートストラップ回路を用いて出力端子の電位を上昇させることにより出力端子から高電源電位を出力し、トランジスタは、チャネルが形成される半導体層と、半導体層を挟んで上下に設けられた一対のゲート電極とを有し、一対のゲート電極の他方はソースと接続される。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】ソース電極層又はドレイン電極層に接する第1の酸化物半導体層と、第1の酸化物半導体層上に設けられ第1の酸化物半導体層とは異なるエネルギーギャップを有する第2の酸化物半導体層と、を少なくとも含む酸化物半導体積層を用いてトランジスタを構成する。第1の酸化物半導体層と第2の酸化物半導体層とは互いに異なるエネルギーギャップを有すればよく、その積層順は問わない。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】酸化物半導体をチャネル形成領域に用いたトランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現するトランジスタ構造を提供する。

【解決手段】異なるエネルギーギャップを有する、少なくとも第1の酸化物半導体層及び第2の酸化物半導体層を積層させた酸化物半導体積層であって、化学量論的組成比よりも過剰に酸素を含む領域を有する酸化物半導体積層を用いてトランジスタを形成する。

(もっと読む)

半導体装置

【課題】プラスチック支持体を用いた半導体装置を提供する。

【解決手段】プラスチック支持体上に形成されたカラーフィルタと、前記カラーフィルタ

上に形成された接着層と、前記接着層上に形成された絶縁膜と、前記絶縁膜上に形成され

た薄膜トランジスタと、前記薄膜トランジスタ上に形成された発光素子とを有する。また

は、プラスチック支持体と、前記プラスチック支持体に対向する対向基板と、前記プラス

チック支持体と前記対向基板との間に保持された液晶とを有し、前記プラスチック支持体

上に形成されたカラーフィルタと、前記カラーフィルタ上に形成された接着層と、前記接

着層上に形成された絶縁膜と、前記絶縁膜上に形成された薄膜トランジスタとを有する。

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

ポリシリコン活性層を含む薄膜トランジスタ及びその製造方法とアレイ基板

【課題】ポリシリコン活性層を含む薄膜トランジスタの製造方法を提供する。

【解決手段】前記製造方法は、基板にアモルファスシリコン層を堆積するとともに、前記アモルファスシリコン層に対してパターニングを行うことで、ソース領域とドレイン領域とチャンネル領域とを含む活性層を形成するステップと、前記ソース領域及び前記ドレイン領域に誘起金属を堆積するステップと、前記誘起金属が堆積された前記活性層に対して第1の熱処理を行い、前記活性層が前記誘起金属の作用によって結晶化されるステップと、前記ソース領域及び前記ドレイン領域に、前記誘起金属を集めるための第1の不純物をドープするステップと、ドープされた前記活性層に対して第2の熱処理を行い、前記第1の不純物が前記チャンネル領域に残された誘起金属に対して吸収するステップと、を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

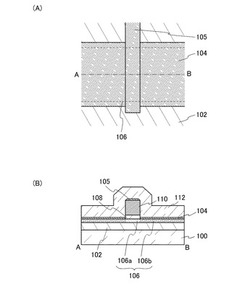

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

1 - 20 / 120

[ Back to top ]