Fターム[5F110HJ22]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物導入後の処理 (2,071)

Fターム[5F110HJ22]の下位に属するFターム

不純物の活性化 (1,881)

Fターム[5F110HJ22]に分類される特許

161 - 180 / 190

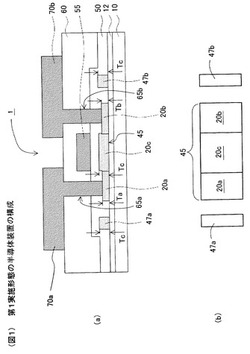

薄膜トランジスタを備えた半導体装置及びその製造方法

【課題】 従来よりも総工程数を減少でき、且つ動作特性及び信頼性を改善することができる半導体装置及びその製造方法を提供することにある。

【解決手段】 基板10に直接または下地膜12を介してアイランド状に形成された、活性層として機能する半導体膜45と、この半導体膜45内に形成された一対のソース・ドレイン領域20a及び20bとを備える。一対のソース・ドレイン領域20a及び20bは、半導体膜45のソース・ドレイン領域20a及び20b以外の部分よりも薄くされており、その厚さの差が10オングストローム〜100オングストロームの範囲内に設定されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】シリコン基板の表面から非常に浅い領域に高濃度の不純物を導入することができる半導体装置の製造方法を提供する。

【解決手段】p型シリコン基板1上の所定の位置に形成された所定形状のゲート絶縁膜4とゲート電極5を含むゲート構造のゲート長方向両側に浅い接合のソース/ドレイン領域を形成する半導体装置の製造方法であって、ソース/ドレイン領域の形成領域を、所定の深さにエッチングするエッチング工程と、p型シリコン基板1上に所定の組成の30Si層を堆積させ、ソース/ドレイン領域の形成領域に30Si層21を選択エピタキシャル成長させる30Si層形成工程と、p型シリコン基板1に中性子線50を照射して、30Si層21中に所定の濃度の31Pを形成する中性子線照射工程と、を含む。

(もっと読む)

薄膜トランジスタ搭載パネルの製造方法

【課題】 レーザーアニールの熱によっても、プラスチック基板上に形成された薄膜トランジスタが、そのプラスチック基板から剥離し難くさせる薄膜トランジスタ搭載パネルの製造方法を提供する。

【解決手段】 プラスチック基板11を熱処理又は真空処理する工程と、熱処理又は真空処理されたプラスチック基板11上にアモルファスシリコン薄膜21aを形成する工程と、アモルファスシリコン薄膜21aをレーザーアニール22してポリシリコン薄膜21pを形成する工程と、ポリシリコン薄膜21pの所定領域に不純物イオンを添加した後にレーザーアニール25することによって熱活性化して不純物拡散領域13s,13dを形成する工程とを有する。熱処理としては、90℃以上200℃以下の範囲内で10分以上の条件で行われることが好ましく、真空処理としては、1×10−3Pa以上1×10−5Pa以下の範囲内で60分以上の条件で行われることが好ましい。

(もっと読む)

薄膜トランジスタ搭載パネル及びその製造方法

【課題】 レーザーアニールによる熱によっても、プラスチック基板上に形成された薄膜トランジスタが、そのプラスチック基板から剥離し難い構造からなる薄膜トランジスタ搭載パネル及びその製造方法を提供する。

【解決手段】 プラスチック基板上に形成されたアモルファスシリコンをレーザーアニールしてポリシリコン薄膜を形成し、そのポリシリコン薄膜の所定領域に不純物イオンを添加した後にレーザーアニールによって熱活性化してなる薄膜トランジスタ搭載パネルであって、プラスチック基板とポリシリコン薄膜との間に、レーザーアニール時にプラスチック基板側に伝わる熱を緩衝する熱緩衝膜を形成する。その熱緩衝膜の厚さをT(μm)、熱緩衝膜の材料の比熱をC(J/(g・K))、熱緩衝膜の材料の比重をρ(g/cm3)、熱緩衝膜の材料の熱伝導率をκ(W/(m・K))としたとき、T≧1.02×κ/(C×ρ)の関係を満たす。

(もっと読む)

半導体装置の製造方法およびMOS電界効果トランジスタ

【課題】基板浮遊効果の抑制、およびオフリーク電流の低減化を、実用上充分なレベルで同時に達成すること

【解決手段】 絶縁体12b上の半導体層12cに設けられたp型の素子形成領域18にイオン注入された、n型の第1ドーパントを、アニールにより活性化することで形成されたソース領域20、ドレイン領域22、およびボディ領域24とを備える半導体装置を製造するにあたり、第1ドーパントのイオン注入に先立ち、(a)ボディ領域の形成予定領域内の領域であって、形成されるべきソースおよびドレイン領域との境界領域へのArのイオン注入と、(b)第1ドーパントの活性化のためのアニールよりも高温で、Arのイオン注入により生じた結晶の欠陥を部分的に回復させるための高温アニールとを行う。

(もっと読む)

薄膜トランジスタ搭載パネル及びその製造方法

【課題】 TFT製造工程中に加わる各種の熱履歴によっても、プラスチック基板上に形成された薄膜トランジスタがそのプラスチック基板とバッファ層との界面剥離に基づいて剥離することのない薄膜トランジスタ搭載パネルを提供する。

【解決手段】 プラスチック基板10上にバッファ層12を介してポリシリコン薄膜13が形成されてなる薄膜トランジスタ搭載パネルにおいて、プラスチック基板10とバッファ層12との間に無機密着層11を形成する。無機密着層11は、クロム、チタン、アルミニウム、シリコン、酸化クロム、酸化チタン、酸化アルミニウム、窒化シリコン、及び酸窒化シリコンの群から選択されるいずれかであることが好ましく、バッファ層12は酸化シリコンであることが好ましい。

(もっと読む)

混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタ

【課題】 混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタを提供すること。

【解決手段】 ハイブリッド配向基板は、n型電界効果トランジスタ(nFET)が電子移動度に最適な半導体の配向内に配置され、p型電界効果トランジスタ(pFET)が正孔移動度に最適な半導体の配向内に配置される、相補型金属酸化膜半導体(CMOS)回路の製造を可能にする。本発明は、最適な半導体の配向内に完全に形成されたFETの性能利点が、デバイスのチャネルを最適な配向をもつ半導体内に配置することを必要とするだけで実現できることを開示する。様々な新しいFET構造体が説明され、その全ては、FETのチャネルは、FETのソース及び/又はドレインとは異なる配向を有するという特徴を備えている。これらの新しいFETを組み込むことができるハイブリッド基板は、その製造方法と共に説明される。

(もっと読む)

シリコンオンナッシング金属酸化物半導体電界效果トランジスタ及びその製造方法

【課題】本発明はシリコン基板内部にブリスター(blister)を形成することで、バルク(bulk)構造及びSOI構造の短所を同時に改善することができるSON(Silicon−On−Nothing) MOSFET及びその製造方法を提供する。

【解決手段】シリコン基板の上部両側に形成された素子分離絶縁膜、素子分離絶縁膜の間のシリコン基板表面に順に形成されたゲート絶縁膜とゲート電極、ゲート絶縁膜と素子分離絶縁膜の間のシリコン基板上部に形成されたソース領域とドレイン領域、ゲート絶縁膜下部のシリコン基板内部に形成されたブリスター、ブリスターとソース領域及びドレイン領域によって取り囲まれるシリコン基板内部のシリコンチャンネルを含み、ブリスターは水素またはヘリウムイオンで形成される。

(もっと読む)

半導体装置の製造方法

【課題】ソース/ドレイン領域におけるシリコンの抵抗率が、トランジスタの性能が得られるほど十分に低下した半導体装置を実現する。

【解決手段】本発明の半導体装置の製造方法では、ガラス基板上にシリコン集積回路を作製する方法であって、ガラス基板を用意する工程14と、ガラス基板上にシリコン層を作製する工程22と、シリコン層の活性領域にイオンを注入する工程42と、シリコン層を熱パッド材で覆う工程50と、ガラス基板をその熱平衡温度以下の温度に保ちながらアニールすることによってシリコン層内のイオンを活性化させる工程52と、熱パッド材を除去する工程54と、シリコン集積回路を完成させる工程56とを含む。

(もっと読む)

高耐圧型半導体装置

【課題】高耐圧型半導体装置の構造の改良を図ることにより“OFF”状態において高耐圧であり、かつ、“ON”状態において低抵抗な高耐圧型半導体装置を提供する。

【解決手段】n-不純物拡散領域4がソース領域3を覆うように形成されている。これにより、n-エピタキシャル層2の空乏層化を促進することができる。したがって、“OFF”状態において、高耐圧が可能な高耐圧型半導体装置を提供することが可能となる。

(もっと読む)

高耐圧型半導体装置

【課題】高耐圧型半導体装置の構造の改良を図ることにより“OFF”状態において高耐圧であり、かつ、“ON”状態において低抵抗な高耐圧型半導体装置を提供する。

【解決手段】ドレイン領域16の内部にn型の不純物拡散領域15が形成され、さらに、ドレイン電極12は、n型の不純物拡散領域15に接続されている。これにより、ドレイン領域16に達したホール電流はn型の不純物拡散領域15に注入される。その結果、このn型の不純物拡散領域15からドレイン領域を通ってn-エピタキシャル層2へ電子電流が流れ出す。したがって、ソース電極11とドレイン電極12との間でホール電流と電子電流が同時に流れる形で高耐圧型半導体装置が“ON”状態となるために、“ON”状態における抵抗を大幅に削減することが可能となる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果によるリーク電流の低減に優れた半導体装置およびその製造方法を提供する。

【解決手段】単結晶半導体基板上に形成された電界効果トランジスタの作成過程において、エクステンション領域を形成するために不純物を導入するとともに、単結晶格子を崩してアモルファス化させる。または、不純物および原子量の大きい元素を導入することによって、単結晶格子を崩してアモルファス化させる。そして、パルス幅が1fs以上10ps以下、かつ波長が370nm以上640nm以下のレーザビームを照射することにより、アモルファス化した部分のみを選択的に活性化させ、エクステンション領域を20nm以下の厚さで形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程に新たな専用工程の追加を伴うことなく、オン抵抗と降伏電圧とのトレードオフの関係(相反関係)を打破して、オン抵抗を低く維持しながら降伏電圧(耐圧)を高めることのできる半導体装置およびその製造方法を提供する。

【解決手段】チャネルとなる不純物領域、すなわちチャネル領域P11についてはこれを、ゲート電極14の直下にあたる部分の不純物濃度が選択的に高められた濃度分布をもつものとし、ドレインとなる不純物領域、すなわちドレイン領域N12についてはこれを、配線とのコンタクト部分(ドレイン層N12b)を除く全域にわたって均一な濃度分布をもつものとする。さらに、チャネル領域P11の近傍にLOCOS酸化膜12を設け、チャネル領域P11に隣接してLOCOS酸化膜12のチャネル側端辺に電流経路を形成するようなドリフト層N12aを形成する。

(もっと読む)

半導体装置、その製造方法、および情報処理装置

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1910は、素子分離領域101と活性領域102とを有する半導体基板100と、活性領域102上にゲート絶縁膜103を介して設けられ、側壁の少なくとも一部がゲート電極側壁絶縁膜105で覆われたゲート電極104と、ゲート電極104の両側にゲート電極側壁絶縁膜105を介してそれぞれ設けられたソース領域106およびドレイン領域106とを備えている。ソース領域106およびドレイン領域106の少なくとも一方は、コンタクト配線と接触するための第2の面を有し、第2の面は、第1の面AA’に対して傾いており、第2の面は、素子分離領域の表面と80度以下の角度で交差する。

(もっと読む)

半導体装置およびその製造方法

【課題】 寄生抵抗が低く、良好な性質を有する半導体装置およびその製造方法を提供する。

【解決手段】 本発明にかかる半導体装置100の製造方法は、(a)絶縁層8上に設けられた半導体層10の上方にゲート絶縁層20を形成する工程と、(b)前記ゲート絶縁層20の上方にゲート電極22を形成する工程と、(c)前記半導体層10に不純物を導入することにより、ソース領域26およびドレイン領域14を形成する工程と、(d)前記半導体層10にフッ素を導入することにより第1のフッ素含有領域50、52を形成する工程と、(e)前記半導体層10の半導体と遷移金属を反応させることにより、低抵抗半導体金属合金層32、34を形成する工程と、を含む。

(もっと読む)

半導体記憶装置

【課題】 情報の読み出し時に、チャネル領域からの多数キャリアの放出による情報の変化と情報の保持時間の短縮を防止し、高速動作の可能な半導体記憶装置を提供する。

【解決手段】 半導体基板3上にチャネル領域4を直立に設け、このチャネル領域4の少なくとも一端にソース/ドレイン層5(6)を設け、チャネル領域4の両側面にゲート絶縁膜7、8を介して第1及び第2のゲート電極9、10を設ける。そして、チャネル領域4に情報の書き込みを行い、その情報の読み出しは、チャネル領域4とソース/ドレイン層5、6間のpn接合を逆方向バイアス状態にしておき、第1及び第2のゲート電極9、10に所定電位を印加することにより両ゲート電極9、10間に流れるトンネル電流量を検知することによって行う。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 真性酸化亜鉛からなる半導体薄膜を有する薄膜トランジスタの製造に際し、加工精度を良くする。

【解決手段】 まず、真性酸化亜鉛からなる半導体薄膜8の上面全体に保護膜9を形成し、その上に上層絶縁膜12を成膜する。次に、上層絶縁膜12および保護膜9にコンタクトホール10、11を形成する。この場合、チャネル長Lは2つのコンタクトホール10、11間の間隔により決定され、チャネル幅Wはコンタクトホール10、11の所定方向の寸法により決定される。これにより、半導体薄膜8にサイドエッチングがやや生じても、チャネル長Lおよびチャネル幅Wに寸法変化が生じることはない。

(もっと読む)

犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【課題】 犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【解決手段】 ゲート積層体(29)と、ゲート積層体(29)の側壁上に配置される1対の第1のスペーサ(32)と、ゲート積層体(29)の両側に配置され、それから第1の間隔を置かれる1対の半導体合金領域(39)とを含む電界効果トランジスタ(FET)(10)が提供される。FET(10)のソース及びドレイン領域(24)は少なくとも部分的に半導体合金領域(39)内に配置され、1対の第1のスペーサ(32)の対応するスペーサによってゲート積層体(29)から、第1の間隔とは異なり得る第2の間隔を置かれる。FET(10)はまた、第1のスペーサ(32)の上に配置される第2のスペーサ(34)と、少なくとも部分的に半導体合金領域(39)の上に重なるシリサイド領域(40)とを含むことができるが、ここでシリサイド領域(40)は第1及び第2のスペーサ(32、34)によってゲート積層体(29)から間隔を置かれる。

(もっと読む)

非対称半導体装置の性能を向上させる方法及び装置

半導体デバイスの性能が向上する方法及び装置が提供される。一実施形態において、第1の電流領域(64、76、23)、チャンネル領域及び第2の電流領域(75、33、66)が互いに隣接している。第2の電流領域(75、33、66)は、第1の電流領域(64、76、23)における第1の元素の含有量より大きい合金の第1の元素の含有量を有し、第2の電流領域(75、33、66)は、チャンネル領域における第1の元素の含有量より大きい第1の元素の含有量を有している。さらに、合金は第2の元素を含み、第1の元素は第1の価電子数を有し、第2の元素は第2の価電子数を有している。さらに、第1の価電子数及び第2の価電子数の合計は8である。  (もっと読む)

(もっと読む)

多結晶シリコンの製造方法及びそれを利用する半導体素子の製造方法

【課題】 良質のpoly−Siの製造及びそれを利用する半導体素子の製造方法を提供する。

【解決手段】 基板1に形成されたa−Si膜3に中性イオンを注入した後、熱処理による多結晶化を行うpoly−Si(多結晶シリコン)、多結晶シリコン層を含んだ半導体素子、及び多結晶シリコン活性層上に形成されたゲート絶縁層上に形成されるゲートを備えたTFTの製造方法であって、熱処理時に高エネルギーであるa−Siを多結晶化でき、一方では、熱に弱いプラスチック等にも良質のpoly−Siを形成でき、シリコン及びガラスのように熱に強い基板、またはプラスチックのように熱に弱い基板に良質の多結晶を形成できる。

(もっと読む)

161 - 180 / 190

[ Back to top ]