Fターム[5F110HJ22]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物導入後の処理 (2,071)

Fターム[5F110HJ22]の下位に属するFターム

不純物の活性化 (1,881)

Fターム[5F110HJ22]に分類される特許

101 - 120 / 190

高応力下にあるチャネルを有するMOSデバイスを製造するための方法

【解決手段】

シリコン含有基板を備えた半導体デバイスを形成するための方法が提供される。1つの例示的な方法は、シリコン含有基板を覆う多結晶シリコン層を堆積させることと、多結晶シリコン層をアモルファス化することと、アモルファス化された多結晶シリコン層をエッチングしてゲート電極を形成することと、ゲート電極を覆う応力誘起層を堆積させることと、シリコン含有基板を焼鈍してゲート電極を再結晶化することと、応力誘起層を除去することと、ゲート電極をエッチングマスクとして用いて基板内へ凹部をエッチングすることと、凹部内に不純物ドープのシリコン含有領域をエピタキシャル成長させることとを備えている。

(もっと読む)

表示装置及び電子デバイス

【課題】反射型表示装置の製造工程を大幅に簡略化する。

【解決手段】薄膜トランジスタと、薄膜トランジスタの上方に配置された絶縁層及び画素電極を有し、画素電極は、薄膜トランジスタに電気的に接続され、表面に凹凸を有し、かつ、反射機能を有し、絶縁層は、酸化珪素、窒化珪素、酸化窒化珪素及び有機性樹脂から選ばれた材料を積層した構造を有し、絶縁層の少なくとも一層はカーボン系材料及び顔料の少なくともいずれか一を含む遮光膜である表示装置とする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

ホウ素閉じ込めを強化した埋め込みSi/Ge材質を有するトランジスタ

【解決手段】

シリコン/ゲルマニウム合金(255)を備えたPチャネルトランジスタのPN接合の近傍に拡散阻害種(256A)を組み込むことによって、拡散関連のPM接合の不均一性を低減することができ、それによりデバイス安定性を高め且つ総合的なトランジスタ性能を高めることに寄与する。拡散阻害種(256A)は炭素、窒素等の形態で提供されてよい。

(もっと読む)

凹状のドレイン及びソース区域並びに非共形的な金属シリサイド領域を有するMOSトランジスタを備えたCMOSデバイス

【解決手段】

凹状のドレイン及びソース構造のトランジスタ(150)における非共形的金属シリサイド層(156)は、歪誘起メカニズム、ドレイン/ソース抵抗等に関して高い性能を提供することができる。このために場合によっては、シリサイド化プロセスに先立ちアモルファス化注入プロセスが実行されてよい一方で、他の場合には高融点金属(156)の異方的な堆積が用いられてよい。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理後も十分に低い電気抵抗率を示し、かつ直接接続された透明画素電極とのコンタクト抵抗が十分に低減されると共に、耐食性および耐熱性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Niを0.05〜0.5原子%、Geを0.4〜1.5原子%、および希土類元素群から選ばれる少なくとも1種の元素を合計で0.05〜0.3原子%含有すると共に、NiおよびGeの合計量が1.7原子%以下である。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗率を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ耐食性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Coを0.05〜0.5原子%、およびGeを0.2〜1.0原子%含み、かつAl合金膜中のCo量とGe量が下記式(1)を満たすことを特徴とする表示装置用Al合金膜。

[Ge]≧−0.25×[Co]+0.2 …(1)

(式(1)中、[Ge]はAl合金膜中のGe量(原子%)、[Co]はAl合金膜中のCo量(原子%)を示す)

(もっと読む)

半導体装置及びその製造方法

【課題】寄生トランジスタによる異常リークの発生を抑制し、正常な電気特性を得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ボロンイオンが導入されたシリコン基板にLOCOS酸化膜2を形成し、この酸化膜2の内側に位置するアクティブ領域1aにおけるチャネル形成領域を含む端部にボロンイオンを注入することにより、アクティブ領域1aにおける前記端部にP型不純物拡散層3を形成し、シリコン基板のアクティブ領域1a上にゲート絶縁膜を形成し、P型不純物拡散層3及びアクティブ領域1aの上にゲート絶縁膜を介してゲート電極6を形成し、LOCOS酸化膜2及びゲート電極6をマスクとして不純物をイオン注入することにより、アクティブ領域にソース・ドレイン領域の拡散層7を形成することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を熱処理することができる半導体装置の製造方法を提供する。

【解決手段】下地層であるpGaN層103に形成された注入領域104’上に、GaNのバンドギャップエネルギーよりも小さいバンドギャップエネルギーを有する物質よりなる光吸収膜T1を形成し、この状態で基板101上面から赤外光や赤色光など、pGaN層103のバンドギャップエネルギーよりも小さいエネルギーの所定光を用いてアニールを行う。pGaN層103と比較して光吸収膜T1の方がアニールで使用される光の吸収係数が大きいため、光吸収膜T1直下もしくは近傍の領域(注入領域104’)を選択的に熱処理することが可能となる。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び表示装置

【課題】静電気による帯電を防止し、素子破壊による不良発生を低減させることができる薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ基板1を製造する各処理工程に長尺プラスチック基板10をロール・ツー・ロールで供給、巻き取りを行いながらその長尺プラスチック基板10の一方の面S1に薄膜トランジスタ50を形成する薄膜トランジスタ基板1の製造方法であって、少なくとも長尺プラスチック基板10の一方の面S1に薄膜トランジスタ50を形成する前に、長尺プラスチック基板10の他方の面S2の全面に導電膜2を形成する。

(もっと読む)

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの特性が設計特性から離れることを抑制できる半導体装置を提供する。

【解決手段】この半導体装置は、チャネル形成領域180上に位置するゲート絶縁膜130及びゲート電極140と、トランジスタのソース及びドレインとして機能する2つの第2導電型高濃度不純物層170と、第2導電型高濃度不純物層170それぞれの周囲に設けられ、第2導電型高濃度不純物層170を深さ方向及びチャネル長方向に拡張し、第2導電型高濃度不純物層170より低濃度である2つの第2導電型低濃度不純物層160と、第2導電型低濃度不純物層160より下に位置し、素子分離膜120の下方を介してチャネル形成領域180の下方から素子分離膜120の外側まで延伸し、半導体層100より高濃度の第1導電型埋込層190を備える。

(もっと読む)

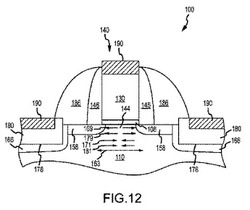

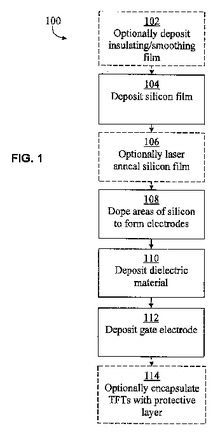

シリコン薄膜トランジスタ、並びにその製造システム及び方法

可撓性基板上に、自己整合シリコン薄膜トランジスタを製造するシステム及び方法。前記システム及び方法は、高いパフォーマンスのトランジスタを製造するために、精密さ、レゾリューション、レジストレーションが達成されるよう、レーザアニール、エッチング技術、レーザドーピングを全て低温度で行いつつ、化学気相堆積、プラズマエンハンスト気相堆積、プリント、コーティング、及び他の堆積処理といった堆積処理を組み込むとともに組み合わせている。そのようなTFTはディスプレイ、パッケージング、ラベリング等に使用できる。  (もっと読む)

(もっと読む)

横型MOS半導体装置

【課題】ボイドのでき易い深いトレンチもしくは経済性の悪い幅広トレンチを形成せずに、高耐圧に必要なオフセットドレイン領域の幅を確保しつつ占有面積を小さくすることができる横型MOS半導体装置を提供すること。

【解決手段】半導体基板の一方側の表面層に、それぞれ一導電型の、ソース領域13とドレイン領域12と、該ドレイン領域12より低不純物濃度で互いに接するオフセットドレイン領域5とを備え、前記ソース領域13表面と前記オフセットドレイン領域5表面に挟まれる他導電型のチャネル領域4表面にゲート絶縁膜を介して設けられるゲート電極6を有する横型MOS半導体装置において、前記オフセットドレイン領域5に、相互に並列で蛇行状の平面パターンであって表面から垂直に形成されるトレンチ列8を備え、該トレンチ列8に電流阻害材料7が充填されている横型MOS半導体装置とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】 オフ電流の突発的な増大が抑制されるTFTを備えた半導体装置を簡便に製造する。

【解決手段】本発明による半導体装置(100)の製造方法は、フォトレジスト層(P)を形成する工程と、導電層(G)に、第1領域(GH)と、第1領域(GH)よりも薄い第2領域(GL)を形成する工程と、フォトレジスト層(P)の一部を除去してフォトレジスト層(P)の残りの部分を除去しないようにフォトレジスト層(P)を部分的にエッチングする工程と、フォトレジスト層(P)の除去しなかった部分(PA’)をマスクとして用いてゲート電極(130)を形成する工程と、導電層(G)の第1領域(GH)および第2領域(GL)に対応して絶縁層(120)の第1領域(120H)および第2領域(120L)を形成する工程とを包含する。

(もっと読む)

半導体装置および半導体装置を製造する方法

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびそれを製造する方法を提供する。

【解決手段】本発明の半導体装置は、素子分離領域と活性領域を有する半導体装置であって、活性領域とゲート酸化膜が接する第1の面より上に、ソース領域およびドレイン領域の一部が存在し、該ソース領域および/または該ドレイン領域と、該ソース領域および/または該ドレイン領域に電気的に接続される電極とが接する第2の面が、該第1の面に対して傾いている。

(もっと読む)

SOI(Silicononinsulator)構造の半導体装置およびその製造方法

【課題】効果的にゲッタリングが行えるSOI構造の半導体装置を提供する。

【解決手段】SOI基板100を用いたSOI構造の半導体装置において、活性層3となるシリコン基板に対してArイオンを注入することにより格子歪み層4を形成する。これにより、格子歪み層4をゲッタリングサイトとして機能させることが可能となる。また、Arイオンのドーズ量を調整し、格子歪み層4の引張り応力が11MPa以上かつ27MPa以下となるようにする。これにより、ゲッタリングサイトとして機能させつつ、リーク電流の発生を抑制することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】薄膜トランジスタを含む半導体装置を歩留まりよく製造するためのアライメントマークを、工程増となることなく、歩留まりと精度のよい半導体装置、及びその製造方法を提供する。

【解決手段】多結晶シリコン半導体膜13と、少なくとも表面が異なるシリコン相6a,6bで図形化されたシリコン膜5からなるアライメントマーク4と、が基板10上に形成されている半導体装置1によって、上記課題を解決する。この異なるシリコン相6a,6bは、多結晶シリコン相6pと非晶質シリコン相6aである。こうした異なるシリコン相6a,6pは、半導体素子部2に多結晶シリコン半導体膜13を形成するためのマスクパターンAを形成するとともに、アライメントマーク部3にアライメントマーク4を形成するためのマスクパターンBを形成し、そのマスクパターンA,B上からイオン注入して、マスクパターンA,Bで覆われていない多結晶シリコン膜の露出部の少なくとも表面を非晶質シリコン相に変化させることによって形成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導体装置を提供する。

【解決手段】基板と、この基板上に設けられた第1の絶縁層と、第1の絶縁層に埋め込まれた導電層と、この導電層に電気的に接続し直上に配置された下部拡散層、この下部拡散層上の半導体層、及びこの半導体層上の上部拡散層を有する柱状半導体部と、前記半導体層の周囲側面に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたゲート電極と、このゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有する半導体装置。

(もっと読む)

101 - 120 / 190

[ Back to top ]