Fターム[5F110HJ22]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物導入後の処理 (2,071)

Fターム[5F110HJ22]の下位に属するFターム

不純物の活性化 (1,881)

Fターム[5F110HJ22]に分類される特許

121 - 140 / 190

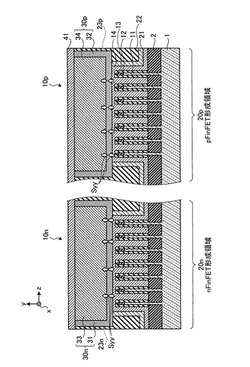

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

特にアナログ適用例に適した電界効果トランジスタを具備する半導体アーキテクチャの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(100,100V,140,150,150V,160,170,170V,180,180V,190,210,210W,220,220U,220W,380,480,500,510,530又は540)は、そのソース/ドレインゾーンと隣接するボディ物質(108,268又は568)との間のPN接合に沿っての寄生容量を減少させるためにそのソース/ドレインゾーンの内の一つ(104,264又は564)下側にハイポアブラプトな垂直ドーパントプロフィルを有している。

【解決手段】 特に、該ボディ物質の導電型を画定する半導体ドーパントの濃度は、そのソース/ドレインゾーンから下方へ該ソース/ドレインゾーンよりも上部半導体表面下側に10倍を超えて一層深いものではない下側のボディ物質位置へ移る場合に、少なくとも10の係数だけ減少する。該ボディ物質は、好適には、他方のソース/ドレインゾーン(102,262又は562)に沿って位置されている一層高度にドープされたポケット部分(120,280又は580)を包含している。通常ドレインとして機能する最初に述べたソース/ドレインゾーン下側のハイポアブラプトな垂直ドーパントプロフィルと、通常ソースとして機能する2番目に述べたソース/ドレインゾーンに沿っての該ポケット部分との結合が、結果的に得られる非対称トランジスタを特に高速アナログ適用例に適したものとさせることを可能とさせる。

(もっと読む)

薄膜半導体素子を備えた表示装置及び薄膜半導体素子の製造方法

【課題】高速動作が可能な高信頼性のアクティブマトリクス方式の表示装置を提供する。

【解決手段】絶縁性基板101上に成膜したSi窒化膜102、Si酸化膜103の上に非晶質Si膜104を成膜する。非晶質Si膜104は脱水素処理される(図1の(a))。この非晶質Si膜104に炭酸ガスレーザーによるアニールと同時にUV光を照射することで結晶化率が90%以上、表面の凹凸差が10nm以下の結晶化Si膜が得られる(図1の(c))。この結晶化Si膜を用いて表示装置のための薄膜トランジスタ等の半導体素子を形成する。炭酸ガスレーザーのみでのアニールでは結晶化率が90%以上の結晶化Si膜を得るためには350℃以上の基板加熱が必要である(図1の(b))。

(もっと読む)

半導体装置の作製方法

【課題】ダングリングボンドの発生を抑制することを課題とする。

【解決手段】半導体膜を形成し、前記半導体膜に、一導電性を有する不純物元素を添加して、前記半導体膜中に、不純物領域、及び、チャネル形成領域を形成し、前記島状半導体上に、ゲート絶縁膜及びゲート電極を形成し、前記半導体膜、ゲート絶縁膜、ゲート電極を覆って、フッ素を含む絶縁膜を形成し、前記半導体膜、前記フッ素を含む絶縁膜を加熱し、前記フッ素を含む絶縁膜を加熱した後に、前記フッ素を含む絶縁膜上に、前記不純物領域に電気的に接続される配線を形成する半導体装置の作製方法に関するものである。前記フッ素を含む絶縁膜は、フッ素を含む酸化珪素膜、フッ素と窒素を含む酸化珪素膜、フッ素を含む窒化珪素膜のいずれか1つである。

(もっと読む)

薄いSOIの集積化のためのMOSトランジスタおよびその製造方法

薄いSOIの集積化のためのMOSトランジスタ(100)およびそのようなMOSトランジスタの製造方法が提供される。1つの例示的方法においては、埋め込み絶縁層(104)を覆うようにシリコン層(106)を設け、このシリコン層上にシリコンを含む材料層(108)をエピタキシャル成長させるステップを含む。このシリコンを含む材料層内にトレンチ(112)がエッチングされ、シリコン層が露出される。MOSトランジスタゲートスタック(148)はトレンチ内に形成される。このMOSトランジスタゲートスタックは、ゲート絶縁体(138)とゲート電極(140)とを含む。ゲートスタックを注入マスクとして使用して、シリコンを含む材料層内に導電性決定型イオン(142)が注入される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

半導体装置の作製方法

【課題】SOI基板の作製時に発生する金属汚染の影響を抑える。

【解決手段】半導体基板に水素イオンを照射し損傷領域を形成した後、ベース基板と半導体基板を接合させる。加熱処理を行って、半導体基板を劈開させSOI基板を作製する。SOI基板の半導体層をエッチングにより素子分離する。素子分離された半導体層に、Arなどの第18族元素と、ドナーまたはアクセプタとなる不純物元素とを添加し、n型またはp型のゲッタリングサイト領域を形成する。加熱処理を行って、半導体層中の金属元素をゲッタリングサイト領域にゲッタリングさせる。水素イオンの照射工程で、水素イオンと共に金属イオンが半導体基板中に打ち込まれても、ゲッタリング処理によって、金属汚染の影響を抑えることができる。したがって、水素イオンの照射をイオンドーピング法で積極的に行うことができる。

(もっと読む)

薄膜トランジスタ、表示装置、及び薄膜トランジスタの製造方法

【課題】ゲート絶縁耐性を向上させる半導体装置を提供する。

【解決手段】本発明に係る半導体装置30は、基板31と、基板31上に形成された絶縁膜(32、33)と、絶縁膜(32、33)上に形成された島状の多結晶半導体層(ポリシリコン層35)と、多結晶半導体層(ポリシリコン層35)上に形成され、純水に対する接触角が10°以下であり、且つ膜厚が0.5nm以下の第1酸化膜36と、第1酸化膜36上に形成されたゲート絶縁膜38と、ゲート絶縁膜38上に形成されたゲート電極39と、を有するものである。

(もっと読む)

表示装置の製造方法

【課題】Al合金膜と透明画素電極との接触電気抵抗を低減でき、耐熱性にも優れているため、Al合金膜を透明画素電極に直接接触させることができ、しかも、Al合金の電気抵抗率も一層低減され、生産性もより高められたダイレクトコンタクト技術を提供する。

【解決手段】基板上にて、酸化物透明導電膜とAl合金膜が直接接触する構造を備えた表示装置の製造方法である。Al合金膜は、Ag、Zn、Cu、およびNiよりなる群から選択される少なくとも一種の合金元素を0.5原子%以下含有し、基板の温度を合金元素の析出温度以上に制御してAl合金膜の形成を行う。

(もっと読む)

表示装置およびスパッタリングターゲット

【課題】バリアメタル層の省略を可能にすると共に、工程数を増やすことなく簡略化し、Al合金膜を導電性酸化膜に対し直接且つ確実に接触することだけでなく、Al合金膜に対し、比較的低い熱処理温度を適用した場合でも、電気抵抗率を低減でき、且つ導電性酸化膜と直接接触したときの接触電気抵抗も低減でき、更には優れた耐熱性と耐食性を達成することのできる技術を提供する。

【解決手段】Al合金膜の上に導電性酸化膜が直接接触する構成を備えた表示装置において、該Al合金膜が、Niを0.05〜2.0原子%と、Inおよび/またはSnを合計で0.05〜1.0原子%含有するように調整する。

(もっと読む)

表示装置の製造方法

【課題】Al合金膜の腐食を抑制できる表示装置の製造方法を提供すること。

【解決手段】Al合金膜上に、フォトリソグラフィー法によって絶縁膜をパターン形成する工程を含む表示装置の製造方法であって、前記Al合金膜は、Alより貴な金属元素を含むものであり、アミン類を含む有機剥離液で絶縁膜上のフォトレジストを除去し、次いでヒドロキシル基とホルミル基とを有する芳香族化合物および/またはヒドロキシル基とカルボキシル基とを有する芳香族化合物を含む洗浄水で洗浄することを特徴とする表示装置の製造方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CMIS構造の半導体装置において、n型およびp型MISEFETの界面抵抗を低減する半導体装置の製造方法および半導体装置を提供する。

【解決手段】第1の半導体領域上にn型MISFETのゲート絶縁膜およびゲート電極を形成し、第2の半導体領域上にp型MISFETのゲート絶縁膜およびゲート電極を形成し、第1の半導体領域にAsをイオン注入して、n型拡散層を形成し、第1の半導体領域上にNiを含む第1の金属を堆積した後、第1の熱処理によって第1のシリサイド層を形成し、第1のシリサイド層上および第2の半導体領域上に、Niを含む第2の金属を堆積した後、第2の熱処理によって、第1のシリサイド層を厚膜化するとともに、第2のシリサイド層を形成し、第2のシリサイド層にBまたはMgをイオン注入した後、第3の熱処理を加えることを特徴とする半導体装置の製造方法および半導体装置。

(もっと読む)

MOSFETアレイにおけるレイアウト依存の閾値電圧変動の迅速な推定方法

集積回路レイアウトにおいて、レイアウトによって誘起される閾値電圧の変動を自動的に推定する方法。前記方法は、解析のために前記レイアウト内の拡散領域を選択する工程で始まる。続いて、システムが、選択された領域のSi/STIエッジと、チャネル領域と、前記チャネル領域に結合するゲート/Siエッジを特定する。次に、特定されたチャネル領域夫々における閾値電圧の変動を特定する。この工程には、縦方向の効果による閾値電圧変動を計算する工程と、横方向の効果による閾値電圧変動を計算する工程と、縦方向と横方向の変動を組み合わせて全体の変動を計算する工程が必要である。最後に、個々のチャネルにおける変動を組み合わせることにより変動の合計が決定される。  (もっと読む)

(もっと読む)

電気光学装置及びその製造方法並びに電子機器

【課題】コンタクト抵抗の低減を図る。

【解決手段】基板上に、導電層402と、透明電極9aと、前記導電層と透明電極との間に形成される層間絶縁膜44と、前記導電層と前記透明電極とをコンタクト部において電気的に接続するために前記層間絶縁膜に開孔されたコンタクトホール89と、少なくとも前記コンタクト部において、前記導電層と前記透明電極との間に設けられる酸化チタン膜17と、を具備したことを特徴とする。

(もっと読む)

絶縁膜の製造方法

【課題】異なる金属酸化膜を複数積層させてなる絶縁膜について、当該絶縁膜の誘電率を高めることができる絶縁膜の製造方法を提供する。

【解決手段】基板11上に、第1の電極12を形成し、その上に、酸化アルミニウム膜と酸化チタン膜とが積層された積層膜よりなる絶縁膜13を形成した後、この絶縁膜13に対して、当該絶縁膜13の透過率が10〜80%になる波長を持つレーザーLを照射する。それにより、絶縁膜13の容量を大きくし誘電率を高める。

(もっと読む)

半導体装置

【課題】ESD耐量を確保できるLDMOSを備えた半導体装置を提供する。

【解決手段】トレンチ4内に絶縁膜5を介してドープトPoly−Si6を配置し、このドープトPoly−Si6がゲート電極12と連結されるようにする。このような構造により、サージが印加されたときに、ゲート電極12にゲート電位を持たせることができ、チャネル領域をオンさせられるため、n+型ドレイン領域10とn+型ソース領域9との間で電流が流れ易くなるようにできる。これにより、サージ電流によりLDMOSが熱破壊されてしまうことを防止することが可能となる。そして、トレンチ4内に埋め込まれたドープトPoly−Si6の不純物濃度を調整し、この抵抗値を変化させることで、ESD耐量を制御することも可能となり、ESD耐量を確保することが可能となる。

(もっと読む)

シリコン酸化膜の形成方法、半導体装置及びその製造方法

【課題】基板表面に、均一な高品質シリコン酸化膜を、基板温度200−500度の低温で形成すること。および、シリコン酸化膜を用いた半導体装置を提供し、素子分離領域凹部分の側壁部のシリコン表面においてシリコン酸化膜の厚さ30%以内に抑え、デバイスの信頼性を向上する。

【解決手段】シリコン酸化膜中にKrを含有することを特徴とする。シリコン酸化膜中にKrを含有させることにより、シリコン酸化膜中および、シリコン/シリコン酸化膜界面でのストレスを緩和することにより、低温で形成したにもかかわらず高品質なシリコン酸化膜を形成し、素子分離領域凹部分の側壁部のシリコン表面においてシリコン酸化膜の厚さの均一性を30%以内にする。

(もっと読む)

端面センサデバイスの製造方法

【課題】形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な端面センサデバイス及びその製造方法を提供すること。

【解決手段】線状体の端面に、対象からの情報を受容して他の情報として出力する受容部が形成されていることを特徴とする端面センサデバイス。線状体2001は、中止部に中心電極2007を有し、その外周は絶縁膜2008で覆われている。上記線状体2001を用意し、その端面にn型半導体層2004を形成する。次いで、n型半導体層2004上にp型半導体層2003を形成する。これにより、線状体2001の端面にpn接合の受容部(光センサ)が形成される。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】特性ばらつきを抑制し、S-factorの低減を図れるポリシリコンSOIを用いた不揮発性メモリを提供する。

【解決手段】基板1と、基板1上に形成した第1の絶縁膜3と、絶縁膜3上にポリシリコンで形成した半導体膜5、5´と、半導体膜5、5´上に形成したトンネル膜9と、トンネル膜9の上に形成した浮遊ゲート11と、浮遊ゲート11上に形成した第2の絶縁膜13と、第2の絶縁膜膜13上に形成した制御ゲート15と、浮遊ゲート11下の半導体膜5、5´を挟むように、半導体膜5、5´を貫通して第1の絶縁膜3上に対向して形成された金属若しくは金属シリサイドからなる導電体領域7とを具備する。

(もっと読む)

薄膜トランジスタ基板

【課題】寸法安定性に乏しいプラスチック基材を用いて薄膜トランジスタ基板を製造する際に加わる熱や雰囲気によっても、薄膜トランジスタを構成する電極や半導体薄膜にクラックが生じることがなく且つ剥離し難い薄膜トランジスタ基板を提供する。

【解決手段】プラスチック基材10と、プラスチック基材10上に形成された無機材料からなる圧縮応力膜12と、圧縮応力膜12上に形成された金属電極膜15又は半導体薄膜13とを少なくとも有するようにして、上記課題を解決した。このとき、圧縮応力膜12の応力値が0.05GPa以上、1.0GPa以下の絶対値を有することが好ましく、圧縮応力膜12が酸化ケイ素膜、窒化ケイ素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸窒化アルミニウム膜及び酸窒化ケイ素の群から選択されるいずれかであることが好ましい。

(もっと読む)

121 - 140 / 190

[ Back to top ]