Fターム[5F110HJ22]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物導入後の処理 (2,071)

Fターム[5F110HJ22]の下位に属するFターム

不純物の活性化 (1,881)

Fターム[5F110HJ22]に分類される特許

141 - 160 / 190

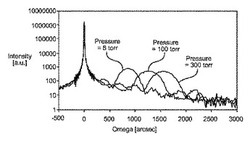

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】 リンでドープされたシリコンと炭素を含有するエピタキシャル層を形成する方法を提供する。

【解決手段】 圧力は、堆積中100トール以上に維持される。方法は、置換型炭素を含む膜の形成を生じさせる。特定の実施形態は、半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおけるエピタキシャル層の形成と処理に関する。

(もっと読む)

半導体素子製造方法

【課題】良好な膜質を有するゲート絶縁膜を化合物半導体層上に形成することができる半導体素子製造方法を提供すること。

【解決手段】本発明は、基板1上にバッファ層2を介して積層されたGaN活性層3とゲート電極8との間にゲート絶縁膜であるSiO2膜5が形成された半導体素子を製造する半導体素子製造方法において、ゲート絶縁膜は、ECRスパッタリング法を用いて形成されることを特徴とする。この結果、良好な膜質を有するゲート絶縁膜をGaN活性層3上に形成することができる半導体素子製造方法を提供することが可能になる。

(もっと読む)

半導体装置およびその製造方法

【課題】接合により形成された単結晶半導体層を有する半導体装置において、単結晶半導体層の接合によって生じる表面段差を低減する。

【解決手段】誘電体基板33に支持された第1および第2の半導体素子100A、100Bを備える半導体装置200の製造方法であって、(c)単結晶半導体基板1の第1主面S1における半導体素子形成領域T1、T2に、活性層領域25A、25Bとをそれぞれ形成する工程と、(d)単結晶半導体基板1に剥離用物質27を注入することにより、単結晶半導体基板1における素子分離領域10よりも第2主面S2の側に剥離層28を形成する工程と、(e)単結晶半導体基板1における剥離層28よりも第2主面S2の側に位置する部分1bを、単結晶半導体基板1から剥離することにより、半導体素子形成領域T1、T2を含む単結晶半導体層1aを得る工程と、(f)単結晶半導体層1のエッチングまたは研磨を行う工程とを包含する。

(もっと読む)

多結晶シリコン膜の製造方法及び製造装置並びに薄膜トランジスタ基板

【課題】シリコン膜の酸化を防ぎ、良好な多結晶シリコン膜を得ることができると共に、絶縁性基板上に低コストで多結晶シリコン膜を形成することが可能な多結晶シリコン膜の製造方法及び製造装置を提供する。

【解決手段】絶縁性基板上に非晶質シリコン膜を非酸化性雰囲気下で形成する非晶質シリコン膜形成工程と、非晶質シリコン膜を非酸化性雰囲気下で多結晶化させる多結晶シリコン膜形成工程と、非晶質シリコン膜形成工程から多結晶シリコン膜形成工程に被処理基板を移行するときの工程であって、非晶質シリコン膜を形成した後に非晶質シリコン膜形成工程の非酸化性雰囲気を大気雰囲気又は所定の酸素分圧を有する雰囲気に変化させ、その後、被処理基板2を多結晶シリコン膜形成工程に移行して、多結晶シリコン膜形成工程内の雰囲気を非酸化性雰囲気に変化させる雰囲気制御工程とを有する。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】基板としてプラスチック基板を用いた薄膜トランジスタ基板の製造工程中で用いられるレジスト膜を除去する際に、プラスチック基板に化学的なダメージを与えない層構成を有した薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】酸素プラズマ耐性のある無機層11が全面に形成されたプラスチック基板10を準備する工程と、無機層11上に半導体膜を形成する工程と、半導体膜上にレジスト膜をパターニングする工程とを有し、レジスト膜の除去工程がプラズマアッシング法により行われる方法により薄膜トランジスタ基板を製造する。このとき、無機層が、クロム、チタン、アルミニウム、シリコン、酸化クロム、酸化チタン、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウム、酸化シリコン、窒化シリコン、及び酸窒化シリコンの群から選択されるいずれかからなることが好ましい。

(もっと読む)

データ記憶回路用非対称性トランジスタ

ソース(30)の抵抗がドレイン(40)よりも高いトランジスタ(22)は、記憶回路(10)におけるプル・アップ素子(20)として最適である。トランジスタは、ソース抵抗を有するソース注入を備えたソース領域を有している。ソース領域はサリサイド化されない。トランジスタの電気伝導を制御するため、制御電極領域(50)がソース領域に隣接している。ドレイン領域(40)は、制御電極領域に隣接すると共に、ソース領域とは反対側に設けられている。ドレイン領域は、ドレイン抵抗を有しサリサイド化されたドレイン注入を有している。ソース領域の物理特性はドレイン領域とは異なるため、ソース抵抗はドレイン抵抗よりも高くなっている。  (もっと読む)

(もっと読む)

TFT基板及びその製造方法、これを用いた表示装置、並びに層間絶縁膜の評価方法

【課題】

本発明によるポリシリコンTFT基板においては、欠陥密度の少ない層間絶縁膜を用いることで、高性能なTFT特性を提供することを目的とする。また、層間絶縁膜のE'センター密度を事前に測定し、TFT特性の予測しておくことで、TFT基板の評価期間を短縮すること。

【解決手段】

基板1上に絶縁膜を形成する工程と、ポリシリコン膜4を形成する工程と、ゲート絶縁膜7を形成する工程と、ゲート電極8を形成する工程と、層間絶縁膜10を形成する工程と、ポリシリコン膜4と接続するソース・ドレイン配線11を形成する工程と、保護膜12を形成する工程とを備え、層間絶縁膜10のE'センター密度を1.0×1018spins/cm3以下とする。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留り低下及びコスト上昇を抑え、かつ、光学的特性を良好に維持しつつ、特性の経時的変化を抑制して高い信頼性を確保する。

【解決手段】ポリシリコン膜にドーパントを注入し、加熱処理によって注入したドーパントを活性化し、ソース領域及びドレイン領域、及びチャネル領域を形成した後、基板温度を、350℃〜420℃の範囲内に保って、3分〜60分の処理時間、基板を水素ガスによるプラズマに晒す。これによって、下地保護膜3を構成する二酸化シリコンは、吸蔵水の含有量が抑えられ、薄膜トランジスタ1の動作温度において、下地保護膜3から水分が不純物として特に半導体膜14へ拡散して、動作特性に悪影響を与えることが防止される。

(もっと読む)

insituまたはexsitu熱処理と組み合わされた改良型電界効果トランジスタ向けのイオン注入(FETデバイスを製造する方法およびFETデバイス)

【課題】所望のドーパント密度プロファイルを達成することができ、アモルファス化される層の厚さが十分に限定され、または歪み緩和のレベルが十分に低く、あるいはこれらがともに達成されるイオン注入法を提供することにある。

【解決手段】本発明は、イオン注入ステップをin situまたはex situ熱処理と組み合わせて、注入誘起性のアモルファス化(超薄シリコン・オン・インシュレータ層のFETのソース/ドレイン(S/D)領域の潜在的な問題)、および歪まされたS/D領域の注入誘起性の塑性緩和(その下の基板層と格子不整合の状態にある埋込みS/D領域によってチャネル歪みが誘起される歪みチャネルFETの潜在的な問題)をともに回避し、またはともに最小化し、あるいは一方を回避し、もう一方を最小化する方法を教示する。第1の実施形態では、イオン注入を高温で実行することによって、イオン注入がin situ熱処理と組み合わされる。第2の実施形態では、熱注入を実行する能力を有する手段を必要としない「デバイデッド−ドーズ−アニール−イン−ビトウィーン」(DDAB)法において、イオン注入がex situ熱処理と組み合わせられる。

(もっと読む)

半導体装置及びその製造方法

【課題】ドレイン電流(Ids)の低下を抑えつつ、ゲート誘起ドレインリーク電流(GIDL)を低減できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】支持基板上に設けられた絶縁層3と、絶縁層3上に設けられた半導体層5とを含む多層膜基板に形成されたトランジスタ100、を有する半導体装置であって、トランジスタ100のゲート電極20とLDD層43とが平面視で重なる第1領域のゲート絶縁膜11bの厚さは、ゲート電極20とそのチャネル領域5aとが平面視で重なる第2領域のゲート絶縁膜11cの厚さよりも大きく形成されている。このような構成であれば、ゲート電極からドレイン中に印加される電界を緩和することができ、ドレインの伝導バンドのエネルギー準位端の曲率を小さくすることができる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ソース・ドレイン領域へのコンタクト抵抗が小さく、かつ、電気的特性が従来よりも安定したFIN型FETからなるメモリセルを備えた半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、絶縁層20と、絶縁層上に設けられ、電気的に浮遊状態のフローティングボディ領域R2、および、該フローティングボディ領域の両側にあるソース・ドレイン領域R1を含むFIN型半導体層45と、フローティングボディ領域の両側面に形成されたゲート絶縁膜50と、フローティングボディ領域の両側面にゲート絶縁膜を介して設けられたゲート電極70と、ソース・ドレイン領域の上面に接触するソース・ドレイン電極SL・BLとを備え、絶縁層の表面と平行にFIN型半導体層を切断した断面において、フローティングボディ領域における該FIN型半導体層の厚みD2が、ソース・ドレイン領域における該FIN型半導体層の厚みD1よりも薄い。

(もっと読む)

半導体装置の製造方法、電子光学装置の製造方法および電子機器の製造方法

【課題】不純物ドープ半導体膜を形成する際の熱負荷を低減する。また、熱負荷を低減することで、TFTの特性を向上させる。

【解決手段】半導体膜3および絶縁膜5を順次形成し、これらの膜よりなる積層膜した後、この積層膜を選択的に除去することにより、プール部7bおよびこのプール部7bに連結した一対の溝7aを形成し、プール部7bにドープ高次シラン組成物溶液9を充填し、この溶液9を溝7a内部に導入した後、熱処理によりドープシリコン膜9Aを形成する。次いで、溝7a間に位置する絶縁膜5上にゲート電極を形成することによりTFTを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜とゲート電極との間に金属粒子を備えた半導体装置において、ゲート電極の仕事関数の調整(閾値電圧の制御)と空乏化の抑制に加え、さらに金属粒子とこの周囲の膜との密着性を向上させた半導体装置を提供する。

【解決手段】 p型シリコン基板1、埋め込み酸化膜2、及び単結晶シリコン層3から構成されるSOI基板4において、単結晶シリコン層3にソース領域10およびドレイン領域11を備える。ソース領域10とドレイン領域11との間の単結晶シリコン層3の表面側はチャネル層3aとして機能する。チャネル層3aの上にはゲート絶縁膜5が形成される。ゲート絶縁膜5上には、窒化チタンからなる金属粒子6aと多結晶シリコン膜7から構成されるゲート電極8が設けられる。ここで、金属粒子6aと多結晶シリコン膜7との間にはチタンシリサイド反応層6bが形成され、金属粒子6aとゲート絶縁膜5との間には反応層6cが形成される。

(もっと読む)

半導体装置の製造方法

【課題】低温における熱処理でもソース/ドレイン領域の不純物活性化が実現でき、高性能な薄膜トランジスタを得ることを可能とする半導体装置の製造方法を提供する。

【解決手段】基板上に半導体膜の結晶化の際の起点となる複数の起点部をソース/ドレイン領域に略単結晶粒が含まれる位置に形成し、起点部が形成された基板上に半導体膜を形成し、半導体膜に熱処理を行い複数の起点部の各々を略中心とする複数の略単結晶粒を形成し、半導体膜をパターニングし、ソース/ドレイン領域及びチャネル形成領域となるトランジスタ領域を形成し、トランジスタ領域上にゲート絶縁膜及びゲート電極を形成し、ゲート絶縁膜及びゲート電極上からイオンを注入してソース/ドレイン領域の一部を非晶質化し、非晶質化されたソース/ドレイン領域に不純物を導入し、

不純物が導入されたソース/ドレイン領域に熱処理を加えソース/ドレイン領域の結晶性を回復させる。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

半導体装置及びその製造方法

【課題】シリコンCMOSデバイス等におけるシングルメタルゲート構造を実現することができ、デバイス特性揺らぎの低減及び高信頼化をはかる。

【解決手段】基板上に、pチャネルMISトランジスタ41とnチャネルMISトランジスタ42を備えた半導体装置であって、pチャネルMISトランジスタ41とnチャネルMISトランジスタ42の各ゲート電極32はTaとCの合金で形成され、ゲート電極32のTaに対するCのモル比(C/Ta)が2以上4以下である。

(もっと読む)

傾斜式プレアモルファス化による歪みトランジスタの結晶欠陥低減化技術

応力のかけられたオーバーライ材料(209、211、309、311、319S)に基づいて傾斜インプランテーションと後続の再結晶化を実行することにより、非常に実効的な応力生成メカニズムが提供される。この傾斜アモルファス化インプランテーション(208、308P、308N)により、再結晶化プロセスにおいて欠陥率が著しく低減し、これにより、高度なトランジスタ素子(200、300N、300Pにおいて、リーク電流が実質的に低減する。  (もっと読む)

(もっと読む)

電界効果トランジスタ(FET)およびその製造方法(高性能および低リーク電界効果トランジスタを製造するための構造および方法)

【課題】ソース側半導体、ドレイン側半導体、およびゲートを含む電界効果トランジスタ(FET)を提供すること。

【解決手段】ソース側半導体は高移動度半導体材料で作製され、ドレイン側半導体は低リーク半導体材料で作製される。一実施形態では、このFETは、金属酸化物半導体電界効果トランジスタ(MOSFET)である。また、このFETの製造方法も提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース/ドレイン間でのリーク電流の発生が防止された半導体装置を提供する。

【解決手段】ゲート電極5およびサイドウォール絶縁膜6は、素子形成領域の上側の領域から素子分離酸化膜2の上側の領域まで延びており、かつ、チタンシリサイド膜は、少なくともサイドウォール酸化膜6および素子分離酸化膜2に隣接する領域であってサイドウォール酸化膜6の外側に位置する領域には形成されていない。

(もっと読む)

ナノワイヤを基礎にした電子デバイスにおけるゲート開閉形態および改良された接点のための方法、システム、および装置

改良ゲート構造を有する電子デバイスのための方法、システムおよび装置が記載される。電子デバイスは、少なくとも1つのナノワイヤを含む。ゲート接点は、少なくとも1つのナノワイヤの長さの一部分に沿って位置決めされる。誘電材料層は、ゲート接点と少なくとも1つのナノワイヤとの間にある。ソース接点およびドレイン接点は、少なくとも1つのナノワイヤと接触している。ソース接点またはドレイン接点の少なくとも一部分は、ナノワイヤ長さに沿ってゲート接点と重複する。電子デバイスは、絶縁シェル層によって取り囲まれた半導体コアを有するナノワイヤを含み得る。リング形状の第1のゲート領域は、ナノワイヤの長さの一部分に沿ってナノワイヤを取り囲む。第2のゲート領域は、ナノワイヤと基板との間のナノワイヤに沿って位置決めされる。ソース接点とドレイン接点は、半導体コアの個々の剥き出た部分でナノワイヤの半導体コアにカップルされる。  (もっと読む)

(もっと読む)

141 - 160 / 190

[ Back to top ]