Fターム[5F110HJ22]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物導入後の処理 (2,071)

Fターム[5F110HJ22]の下位に属するFターム

不純物の活性化 (1,881)

Fターム[5F110HJ22]に分類される特許

61 - 80 / 190

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域の形成は、チャネル保護層をマスクとして半導体層に希ガスまたは水素のうち、一種類または複数種類の元素をイオンドーピング法またはイオンインプランテーション法により行う。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

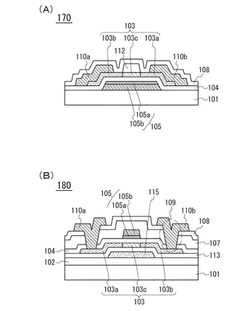

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電界効果移動度が大きい酸化物半導体層を用いた半導体装置の作製方法を提供することを課題の一つとする。また、高速動作可能な半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層をハロゲン元素により終端化させて、酸化物半導体層と、酸化物半導体層と接する導電層のコンタクト抵抗の増大を抑制することで、酸化物半導体層と導電層のコンタクト抵抗が良好になり、電界効果移動度が高いトランジスタを作製することができる。

(もっと読む)

半導体基板、電界効果トランジスタ、集積回路、及び半導体基板の製造方法

【課題】絶縁膜を介在させて基板同士を貼り合わせることで、一方の基板上に形成された半導体層を他方の基板に形成できると共に、この際に当該半導体層の結晶構造を損傷させることなく、高品質な結晶構造を維持したまま簡単に製造できる半導体基板、電界効果トランジスタ、集積回路、及び半導体基板の製造方法を提案する。

【解決手段】MISFET1では、InP基板12上のIII-V族化合物半導体層7に、ALD法を用いて表面が平坦な酸化膜6を形成するようにしたことで、当該酸化膜6とSi基板2とを常温において貼り合わせるだけで、これら酸化膜6とSi基板2とを強固に接合でき、かくして一方のInP基板12上に形成されたIII-V族化合物半導体層7を他方のSi基板2に形成できると共に、III-V族化合物半導体層7の結晶構造を損傷させることなく高品質に維持したまま簡単に製造できる。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

誘電体分離型半導体装置の製造方法

【課題】耐圧を向上させることができ、かつ半導体基板が反るのを防ぐことができる誘電体分離型半導体装置の製造方法を得る。

【解決手段】p型シリコン基板10の主面の領域42に複数のトレンチ溝44を形成する。p型シリコン基板10の表面を酸化して、p型シリコン基板10の主面に誘電体層12を形成し、領域42に厚膜誘電体層38を形成する。p型シリコン基板10に誘電体層12を介してn−型半導体層14を貼り合せる。厚膜誘電体層38の上方においてn−型半導体層14の一部にn+型半導体領域18を形成する。n+型半導体領域18から離間してn+型半導体領域18を取り囲むようにn−型半導体層14の一部にp+型半導体領域20を形成する。n+型半導体領域18に接続された主電極26を形成する。p+型半導体領域20に接続された主電極28を形成する。p型シリコン基板10の裏面に裏面電極32を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性が得られるフィン型半導体領域を有する半導体装置を実現する。

【解決手段】上面及び側面を有する第1の半導体領域61の上部に第1導電型の第1の不純物領域61aが形成されていると共に、第1の半導体領域61の側部に第1導電型の第2の不純物領域61bが形成されている。第1の半導体領域61の所定の部分における少なくとも側面及び上部コーナーを覆うようにゲート絶縁膜62が形成されている。ゲート絶縁膜62の外側に位置する部分の第1の半導体領域61における上部コーナーの曲率半径r’は、ゲート絶縁膜62の下側に位置する部分の第1の半導体領域61における上部コーナーの曲率半径rよりも大きく且つ2r以下である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供することを課題の一とする。高速応答及び高速駆動の可能なトランジスタを有する高機能の半導体装置を提供することを課題の一とする。

【解決手段】酸化物半導体を有するトランジスタにおいて、酸化物半導体層に酸素欠陥誘起因子を導入(添加)することによってソース領域及びドレイン領域を選択的に低抵抗化する。酸化物半導体層に酸素欠陥誘起因子を導入することによって、酸化物半導体層にドナーとして機能する酸素欠陥を効果的に形成することができる。導入する酸素欠陥誘起因子としては、チタン、タングステン、及びモリブデンのいずれか一または複数から選択される金属元素を用いてイオン注入法によって導入することが好ましい。

(もっと読む)

半導体装置、表示装置、液晶テレビジョン装置、及びELテレビジョン装置

【課題】より良好な電気的特性を有する化合物半導体を用いた薄膜トランジスタを有する

半導体装置、及びその作製方法を提供することを目的とする。

【解決手段】半導体層として化合物半導体材料を用い、半導体層とソース電極層及びドレ

イン電極層との間に、それぞれ導電性の有機化合物及び無機化合物を含むバッファ層を形

成する。バッファ層は有機化合物及び無機化合物を含む層として形成される。化合物半導

体材料を用いた半導体層とソース電極層及びドレイン電極層との間に介在するバッファ層

によって、半導体層とソース電極層及びドレイン電極層との導電性は向上し、電気的に良

好な接続を行うことができる。

(もっと読む)

電子書籍

【課題】安定した電気的特性を有する薄膜トランジスタを有する表示パネルを供えた電子書籍を提供する。また、画像の保持特性の高い電子書籍を提供する。また、高解像度の電子書籍を提供する。また、消費電力の低い電子書籍を提供する。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル形成領域が形成される薄膜トランジスタによって、電子書籍の表示パネルの表示を制御するものである。

(もっと読む)

61 - 80 / 190

[ Back to top ]