Fターム[5F110HK09]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | Si (2,015)

Fターム[5F110HK09]に分類される特許

141 - 160 / 2,015

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

薄膜トランジスタ

【課題】電気特性の変動が少なく、信頼性の高いトランジスタを提供する。また、電気特性の変動が少なく、信頼性の高いトランジスタを、生産性高く作製する。また、経年変化の少ない表示装置を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース領域及びドレイン領域として機能する不純物半導体膜との間に、微結晶半導体領域及び一対の非晶質半導体領域を有する半導体積層体を有し、微結晶半導体領域は、ゲート絶縁膜側の窒素濃度が少なく、非晶質半導体に接する領域の窒素濃度が高く、且つ非晶質半導体との界面が凹凸状である。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】マスク数が少なく、工程が簡略な半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜と、半導体膜と、不純物半導体膜と、導電膜と、をこの順に積層して形成し、導電膜を加工してソース電極及びドレイン電極を形成し、不純物半導体膜を離間させつつ半導体膜の上部を加工してソース領域及びドレイン領域と、ソース領域及びドレイン領域と重畳しない部分の上部が除去された半導体層と、を形成し、ゲート絶縁膜、半導体層、ソース領域及びドレイン領域、ソース電極及びドレイン電極上にパッシベーション膜を形成し、パッシベーション膜上にエッチングマスクを形成し、エッチングマスクにより、ソース電極またはドレイン電極に達する開口部を形成しつつ、少なくともパッシベーション膜と半導体層を島状に加工し、エッチングマスクを除去し、ゲート絶縁膜及びパッシベーション膜上に画素電極を形成する。

(もっと読む)

薄膜トランジスタおよび画像表示装置

【課題】ホールの多数発生を抑制し、かつリーク電流の増大を抑制することができる薄膜トランジスタを提供する。

【解決手段】本発明に係る薄膜トランジスタでは、半導体層12は、平面視において、ゲート電極2の端辺部2A,2Bからソース電極7およびドレイン電極8が引き出された部分において、ゲート電極2から外側に延在する延在部P1,P2,P3を有している。また、平面視において、ソース電極7とゲート電極2の端辺部2A,2Bとが交差する部分L1,L2は、チャネル形成領域13に接するソース電極7の部分LSと、チャネル長方向Yにおいて重ならない。さらに、平面視において、ドレイン電極8とゲート電極2の端辺部2Bとが交差する部分L3は、チャネル形成領域13に接するドレイン電極8の部分LDと、チャネル長方向Yにおいて重ならない。

(もっと読む)

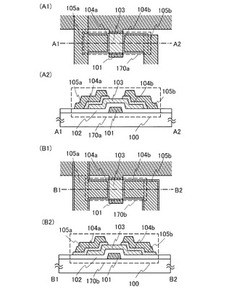

液晶表示装置

【課題】画素内におけるTFTのON電流を増大させ、かつ、ON電流のばらつきを抑える。

【解決手段】TFTにおける半導体層103と1層目のn+a−Si層14をプラズマCVDによって連続して形成する。半導体層103と1層目のn+a−Si層104を同時にパターニングする。その後、2層目のn+a−Si層105を1層目のn+a−Si層104の上と、半導体層103の側部を覆うように形成する。半導体層103の上に連続して1層目のn+a−Si層104を形成することによってTFTのON電流を増大させることが出来るとともに、ON電流のばらつきを小さくすることが出来る。

(もっと読む)

半導体デバイス形成用基板の製造方法及びドライエッチング方法

【課題】絶縁膜上に形成されたレジスト膜の際まで絶縁膜を除去することができる半導体デバイス形成用基板の製造方法及びドライエッチング方法を提供する。

【解決手段】レジスト膜から露出されている絶縁膜を、COF2と酸素とを含む混合ガスをエッチングガスに用いたドライエッチングにより除去する工程を含む半導体デバイス形成用基板の製造方法であって、絶縁膜を除去する工程はCOF2と酸素との流量比(COF2/酸素)が第1の値に設定された第一のドライエッチング工程700と、COF2と酸素との流量比が第1の値よりも大きい第2の値に設定された第二のドライエッチング工程750と、を含む。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

薄膜トランジスタ、表示装置、及び液晶表示装置

【課題】正孔電子対と、ソース電極(ドレイン電極)付近に発生する強電界とがともに抑制されることにより、リーク電流が抑制される薄膜トランジスタ、及びそれを備える表示装置又は液晶表示装置の提供。

【解決手段】光源から光が照射されるゲート電極膜と、前記ゲート電極膜の、前記光源側との反対側に、絶縁膜を介して形成される半導体膜と、前記半導体膜に電気的に接続して形成される第1及び第2の電極膜と、前記ゲート電極膜と同一層に形成されるとともに、前記ゲート電極膜と電気的に遮断される第1の遮光膜と、を備える薄膜トランジスタであって、前記第1の遮光膜は、前記半導体膜の一部と前記光の照射方向から見て重なり合うとともに、前記第1の電極膜の少なくとも一部と、前記光の照射方向から見て重なり合う、ことを特徴とする。

(もっと読む)

表示装置、及び、その製造方法

【課題】薄膜トランジスタにおいて生じるリーク電流を抑えつつ、表示装置の生産性を向上させることを目的とする。

【解決手段】基板301と、基板301に形成されている複数の薄膜トランジスタTFTと、を有する表示装置であって、薄膜トランジスタTFTは、ゲート電極303と、ゲート電極303の上側に配置される微結晶半導体層305と、微結晶半導体層305上に配置される非晶質半導体層306と、を有し、非晶質半導体層306の水素濃度が、12atom%以下である、ことを特徴とする表示装置。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 製造工程を単純化すると同時に、良好な画質を確保できる薄膜トランジスタ表示板を提供することである。また、本発明の他の目的は、画素の開口率を向上することができる薄膜トランジスタ表示板を提供することである。

【解決手段】 本発明の実施形態による薄膜トランジスタ表示板は、基板上に形成されているゲート線と、ゲート線上に形成されているゲート絶縁膜と、ゲート絶縁膜上に形成されている第1半導体と、少なくとも一部分の第1半導体上に形成されているデータ線及びドレイン電極と、ゲート絶縁膜上に形成されている蓄積導電体と、データ線、ドレイン電極及び蓄積導電体上に形成されている第1保護膜と、第1保護膜上に形成され、蓄積導電体上に位置した開口部を有する第2保護膜と、第2保護膜上に形成され、ドレイン電極に接続され、開口部で蓄積導電体と重なる画素電極とを備えることを特徴とする薄膜トランジスタ表示板。

(もっと読む)

トランジスタ、発光装置、及び、電子機器

【課題】トランジスタ外部からの光による悪影響を軽減又は防止したトランジスタ、発光装置、及び、電子機器を提供する。

【解決手段】トランジスタTrは、ゲート電極12と、透光性を有する絶縁層を介してゲート電極12と対向配置される、ゲート電極12側の面に光の反射面を有する導電体層22と、ゲート電極12と導電体層22との間に位置し、チャネルが形成される半導体層14と、を備える。光を吸収する光吸収層21は、導電体層22と半導体層14との間、並びにゲート電極12と半導体層14との間の少なくともいずれか一方に位置する。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】透明導電膜にピンホール等の欠陥が生じたとしても金属導電膜の腐食を抑制し、透明導電膜と金属導電膜との間の導通を確実にとることが可能な薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】金属導電膜としてのゲート端子121、ドレイン端子122上にOC−SiN膜109を形成し、ゲート端子121及びドレイン端子122が露出するようにコンタクトホールを形成し、コンタクトホールを介してゲート端子121及びドレイン端子122に接触するようにITO膜を成膜してパターニングし、ITO膜に対して酸化膜形成処理を行う。これにより、ITO膜にピンホール等の欠陥が発生していた場合には、欠陥を介してITO膜下のゲート端子121ドレイン端子122の一部が酸化されて酸化膜が形成される。

(もっと読む)

半導体装置及びその作製方法

【課題】電極の表面へのエッチングによるダメージを低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第1の絶縁層乃至第3の絶縁層に開口部が設けられたデュアルゲート型トランジスタの第1の絶縁層の厚さと第2の絶縁層の厚さを概ね等しいものとする。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】結晶性半導体膜に対する非晶質半導体膜のエッチング選択比が高いエッチング方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、Br系ガスと、F系ガスと、酸素ガスの混合ガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを行うことで、露出された部分の膜減りを抑えることができる。更には、当該エッチング方法を薄膜トランジスタのバックチャネル部を形成するエッチングに採用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。該薄膜トランジスタ上には絶縁層が設けられていることが好ましい。

(もっと読む)

表示装置

【課題】

表示装置の高解像度化や小型化、さらには画素の開口率の向上を行った場合でも、半導体層に入射する光を効果的に遮断し、ホトコン電流による表示品質の低下を防止することが可能な表示装置を提供すること。

【解決手段】

前記基板上に、第1絶縁膜と、ゲート電極と、ゲート電極の上層に形成された第2絶縁膜と、前記第2絶縁膜の上層に形成された半導体層とが積層され、前記第1絶縁膜は開口部を有し、前記ゲート電極は、前記開口部に倣って形成された窪みを有し、前記半導体層の全部、又は前記半導体層の端部は、平面的に見て前記窪みと重畳していることを特徴とする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び発光装置

【課題】薄膜トランジスタのオン電流の安定を図ること。

【解決手段】ELパネル1の駆動トランジスタ6において、ソース電極6iとゲート電極6aおよびドレイン電極6hとゲート電極6aの間にバックゲート効果を発現させないように、ソース電極6iとドレイン電極6hをゲート電極6aから離間させることに十分な膜厚(例えば、2000Å以上4000Å以下の膜厚)を有する保護絶縁膜6dを形成することによって、駆動トランジスタ6のチャネルが乱されることを低減して、オン電流を安定させるようにした。

(もっと読む)

141 - 160 / 2,015

[ Back to top ]