Fターム[5F110HK09]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | Si (2,015)

Fターム[5F110HK09]に分類される特許

161 - 180 / 2,015

半導体装置及びその作製方法

【課題】電極の表面へのエッチングによるダメージを低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第1の絶縁層乃至第3の絶縁層に開口部が設けられたデュアルゲート型トランジスタの第1の絶縁層の厚さと第2の絶縁層の厚さを概ね等しいものとする。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】結晶性半導体膜に対する非晶質半導体膜のエッチング選択比が高いエッチング方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、Br系ガスと、F系ガスと、酸素ガスの混合ガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを行うことで、露出された部分の膜減りを抑えることができる。更には、当該エッチング方法を薄膜トランジスタのバックチャネル部を形成するエッチングに採用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。該薄膜トランジスタ上には絶縁層が設けられていることが好ましい。

(もっと読む)

表示装置

【課題】

表示装置の高解像度化や小型化、さらには画素の開口率の向上を行った場合でも、半導体層に入射する光を効果的に遮断し、ホトコン電流による表示品質の低下を防止することが可能な表示装置を提供すること。

【解決手段】

前記基板上に、第1絶縁膜と、ゲート電極と、ゲート電極の上層に形成された第2絶縁膜と、前記第2絶縁膜の上層に形成された半導体層とが積層され、前記第1絶縁膜は開口部を有し、前記ゲート電極は、前記開口部に倣って形成された窪みを有し、前記半導体層の全部、又は前記半導体層の端部は、平面的に見て前記窪みと重畳していることを特徴とする。

(もっと読む)

半導体装置

【課題】良好な電気特性を有する半導体装置を提供する。

【解決手段】基板上に形成される第1の電極と、第1の電極に接して形成される一対の酸化物半導体膜と、一対の酸化物半導体膜に接する第2の電極と、少なくとも第1の電極および一対の酸化物半導体膜を覆うゲート絶縁膜と、ゲート絶縁膜に接して、少なくとも一対の酸化物半導体膜の間に形成される第3の電極とを有する半導体装置であり、酸化物半導体膜のドナー密度が1.0×1013/cm3以下である場合、酸化物半導体膜の膜厚は、酸化物半導体膜の膜厚横方向の長さに対して厚くすることである。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、基板10と第1絶縁膜11の間に駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、第2絶縁膜12とパッシベーション膜14の間にスイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜6e(5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】レジストの広がりを容易に制御して、寄生容量の増加を抑制する。

【解決手段】ゲート電極11aa上に、ゲート絶縁膜12、第1半導体膜13、第2半導体膜14及び金属膜を成膜し、金属膜上にレジストを形成する工程と、レジストから露出する金属膜、及びレジストの薄膜部の下層に配置する金属膜の上層部をエッチングしてソースドレイン形成層15aを形成する工程と、レジストRbbから露出するソースドレイン形成層15a及び第2半導体膜14の温度差に基づいてリフロー処理を行いレジストRbcに変形する工程と、レジストRbcを用いて第1半導体層13a及び第2半導体層形成層14aを形成する工程と、レジストRbcを除去した後に、ソース電極及びドレイン電極を形成し、両電極から露出する第2半導体層形成層14aをエッチングして第2半導体層14bを形成する工程とを備える。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

微結晶シリコン膜の作製方法および薄膜トランジスタの作製方法

【課題】絶縁膜と微結晶シリコン膜との密着性を向上させた微結晶シリコン膜の作製方法を提供する。

【解決手段】絶縁膜55上に、後のプラズマ酸化等により完全に酸化される高さ(例えば0nmより大きく5nm以下)の微結晶シリコン粒、または後のプラズマ酸化等により完全に酸化される膜厚(例えば0nmより大きく5nm以下)の微結晶シリコン膜もしくはアモルファスシリコン膜を形成し、前記微結晶シリコン粒または前記微結晶シリコン膜もしくはアモルファスシリコン膜に酸素を含むプラズマ処理またはプラズマ酸化を施すことにより、前記絶縁膜上に酸化シリコン粒57aまたは酸化シリコン膜を形成し、前記酸化シリコン粒または前記酸化シリコン膜の上に微結晶シリコン膜59を形成する微結晶シリコン膜の作製方法である。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

TFTアレイ構造及びその製造方法

【課題】TFTアレイ基板及びその製造方法を提供する。

【解決手段】透明ガラス基板11と、上方に順次ゲート絶縁層13、半導体層14、オーミック接触層15が被覆しているゲートライン12b及びゲートライン12bと一体となるゲート電極12aと、ゲートライン12b及びゲート電極12a、ゲート絶縁層13、半導体層14、オーミック接触層15の両側に形成された絶縁層16と、オーミック接触層15に形成され、半導体層14の中間位置の上方でオーミック接触層15を分断する分断溝15aと、絶縁層16及びオーミック接触層15の上方に形成されたデータライン及び第1、第2のソース・ドレイン電極と、を備えるTFTアレイ基板であり、該TFTアレイ基板はスリットフォトリソグラフィー処理を使用しない4回のフォトリソグラフィー処理により製造できる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】微結晶シリコンを備える薄膜トランジスタにおいて、光リーク電流、及び、電界起因のリーク電流を抑制することが可能な技術を提供することを目的とする。

【解決手段】薄膜トランジスタは、ゲート電極2上にゲート絶縁膜6を介して順に形成された微結晶シリコン膜8、非晶質シリコン膜9、及び、N型非晶質シリコン膜10を含む半導体層25と、微結晶シリコン膜8の端部8bと接触し、かつ、N型非晶質シリコン膜10と接続されたドレイン電極12とを備える。半導体層25は、平面視においてゲート電極2の外周よりも内側に形成され、微結晶シリコン膜8の端部8bは、N型非晶質シリコン膜10と同じN型の導電型を有する。

(もっと読む)

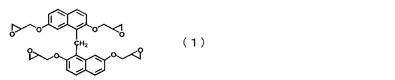

半導体素子基板

【課題】低誘電率特性、低リーク電流特性、および高絶縁破壊電圧特性に優れ、しかも、透明性が高い樹脂膜を備える半導体素子基板を提供すること。

【解決手段】バインダー樹脂(A)、酸性基を有する化合物(B)、架橋剤(C)を含有してなる樹脂組成物からなる樹脂膜を有する半導体素子基板であって、前記架橋剤(C)は、分子量が100〜500であり、かつ、前記架橋剤(C)のSP値をSP1とし、SP値が19620(J/CUM)1/2であるアリルグリシジルエーテルのSP値をSP2とした場合に、SP1−SP2=−1900〜5400(J/CUM)1/2の関係にあるSP値を有し、前記バインダー樹脂(A)100重量部に対する、前記架橋剤(C)の含有量が1〜500重量部であり、前記樹脂膜は、前記半導体素子基板に実装されている半導体素子表面、または前記半導体素子に含まれる半導体層と接触して形成されており、該樹脂膜中の無機イオン含有量が1〜1000ppbであることを特徴とする半導体素子基板を提供する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を形成した後、種結晶上に、第2の条件により種結晶の混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Paより大きく13332Pa以下とする条件である。第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

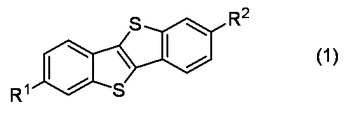

電界効果トランジスタ及びその製造方法

【課題】半導体材料として特定の有機複素環化合物を用いて、実用的な印刷適性を有し、さらにキャリア移動度、ヒステリシスや閾値安定性などの優れた半導体特性を有し、産業上実用的な特定のトップゲート構造の電界効果トランジスタを提供する。

【解決手段】半導体材料として下記式(1)で表される化合物を含有し、特定のトップゲート−ボトムコンタクト構造を有することを特徴とする電界効果トランジスタ。

(式(1)中、R1及びR2はそれぞれ独立に無置換またはハロゲノ置換C1−C36脂肪族炭化水素基を表す。)

(もっと読む)

薄膜トランジスタの製造方法及び薄膜トランジスタ

【課題】トランジスタ特性の改善を図ることができる薄膜トランジスタの製造方法及び薄膜トランジスタを提供する。

【解決手段】活性層30は、第1の半導体膜3cと第2の半導体膜3aの積層構造を有する、第1の半導体膜3cは、アモルファス又は結晶性のシリコン膜にレーザを照射することで形成された微結晶シリコン膜で構成される。微結晶シリコン膜はアモルファスシリコン膜と比較して高いキャリア移動度を得ることができる。第2の半導体膜3aは、ソース/ドレイン電極5a、5dのパターニング工程から第1の半導体膜3cを保護する機能を有している。これにより、第1の半導体膜3cの所期の形状、膜厚を維持して、安定したトランジスタ特性を確保することが可能となる。

(もっと読む)

161 - 180 / 2,015

[ Back to top ]