Fターム[5F110HK09]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | Si (2,015)

Fターム[5F110HK09]に分類される特許

2,001 - 2,015 / 2,015

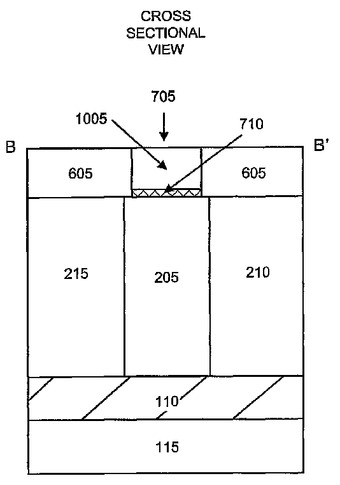

細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET

フィン(205)を形成するステップと、このフィン(205)の一端上にソース領域(210)、このフィン(205)の他端上にドレイン領域(215)を形成するステップとを含む、フィン電界効果トランジスタを形成する方法である。この方法は、フィン(205)上に、第1パターンで、第1半導体材料のダミーゲート(505)を形成するステップと、このダミーゲート(505)の周りに絶縁層(605)を形成するステップをさらに含んでいる。この方法はまた、第1パターンに対応する絶縁層(605)中にトレンチ(705)を残すように、第1半導体材料を除去するステップと、トレンチ(705)内に露出したフィン(205)の部分を細型化するするステップと、トレンチ(705)内に金属ゲート(1005)を形成するステップと、を含んでいる。  (もっと読む)

(もっと読む)

導電性ポリマーの堆積

有機層の作成の前に、沈殿剤を有機電子デバイスの下側電極層に堆積させる。沈殿剤が堆積した後に、有機材料を前記沈殿剤上に堆積させる。前記有機材料を処理された表面上で乾燥して膜にする場合に、前記沈殿剤がより均一でかつより平坦なプロフィールを生じさせる。  (もっと読む)

(もっと読む)

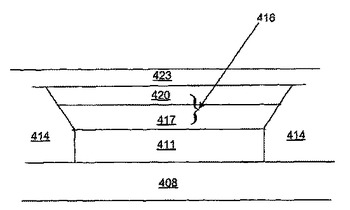

犠牲注入層を用いて非晶質ではない超薄膜半導体デバイスを形成させるための方法

半導体デバイスを形成させるための方法は、単結晶基板(106)の上に犠牲層(108)を定めることを含む。単結晶基板(106)が実質的に非晶質化されないように、ドーパント化学種を犠牲層(108)に注入する。前記ドーパント化学種を前記犠牲層(108)から前記単結晶基板(106)中に移動させるように、犠牲層(108)をアニールする。 (もっと読む)

二重ゲートトランジスタ半導体製造プロセス用の限定スペーサ

半導体製造プロセスは、基板上にシリコンフィンを形成することを含む。フィンの主面上にはゲート誘電体が形成される。フィンの少なくとも2つの面の上にゲート電極が形成される。次いで、ゲート電極の側壁に近接して誘電体スペーサが選択的に形成されて、誘電体スペーサが該側壁に限定されることによって、主フィン面の大部分が露出したままとされる。その後、主フィン面上にシリサイドが形成される。一実施形態では、ゲート電極の形成は、フィンおよび基板の上にポリシリコンを堆積し、ポリシリコンの上にキャッピング層を堆積し、キャッピング層の上にフォトレジストをパターニングし、パターニングしたフォトレジストが適所に配された状態でキャッピング層およびポリシリコンをエッチングすることを含む。エッチングによりポリシリコンの幅はキャッピング層の幅よりも小さくなり、ポリシリコンの側壁に隣接するキャッピング層の下に空隙ができ、ここに限定スペーサを形成することができる。  (もっと読む)

(もっと読む)

Si:CおよびSiGeエピタキシャル成長ソース/ドレインを用いた高性能で応力が向上されたMOSFETおよび製造方法

【課題】 半導体デバイスおよび半導体デバイスの製造方法を提供する。

【解決手段】 半導体デバイスはpFETおよびnFETのためのチャネルを含む。SiGe層はpFETチャネルのソースおよびドレイン領域に選択的に成長され、Si:C層はnFETチャネルのソースおよびドレイン領域に選択的に成長される。SiGe層およびSi:C層は、下に位置するSi層の格子ネットワークに一致して応力成分を生成する。1つの実施形態では、これによって、pFETチャネルでは圧縮成分が引き起こされ、nFETでは引張成分が引き起こされる。

(もっと読む)

分離領域を有する半導体デバイスを形成するための方法

分離構造を有する半導体デバイス(10)を形成するための方法が漏れ電流を低減する。チャネル分離構造(32、30、34)がチャネル構造の中の漏れ電流を低減する。さらに、電流電極領域の下に電流電極誘電体分離構造(36)が形成され、電流電極(40)間の漏れを防ぐ。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

線パターン形成方法、デバイスとその製造方法及び電気光学装置並びに電子機器

【課題】複数の線パターンの形成領域から一時的に溢れ出した機能液同士が接触しないように機能液を吐出することによって短絡を防止すると共に、線パターンと線パターンとをより近接させる。

【解決手段】線パターンの形成方法であって、隣合うバンク間34から一時的に溢れ出した上記機能液X同士が接触しないように各上記バンク間34の幅方向の中央Aに対し当該幅方向に変位した位置を各々のバンク間34の吐出位置として上記機能液Xを吐出することによって複数の上記バンク間34に同時に機能液を配置する。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法並びに液晶表示装置

【課題】 本発明の目的は、液晶配向の不良を減少させ、開口率を高めることにある。

【解決手段】 第1絶縁基板と、第1絶縁基板上部に形成されており、ゲート電極を有するゲート線と、ゲート線を覆うゲート絶縁膜と、ゲート絶縁膜上部に形成されている半導体層と、半導体層上部に形成されているソース電極及びドレイン電極とソース電極に連結されており、ゲート線と交差するデータ線と、有機絶縁膜からなっており、ドレイン電極を露出する第1接触孔を有する保護膜と、第1接触孔を通じてドレイン電極と連結されている画素電極と、第1絶縁基板と対向する第2絶縁基板と、ゲート線またはデータ線と重なるブラックマトリックスと、第1絶縁基板と第2絶縁基板の間でブラックマトリックスと重なって位置し、写真エッチング工程で形成された基板スペーサとを含む液晶表示装置を提供する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

積層金属配線及び薄膜トランジスタ基板、並びにそれらの製造方法

【課題】 IC等の半導体装置や、表示装置に用いられるTFT基板で使用される、Alを含む積層配線の信頼性を高める。

【解決手段】 上層の金属層22を下層のAl又はAlを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させる。この積層配線は、エッチングによりこれを作製する際に、上層の金属層22よりも下層のAl又はAlを含む合金の材料層21の方のエッチング速度を大きくして、Al又はAlを含む合金の材料層21のサイドエッチングを多くし、上層の金属層22を下層のアルミニウム又はアルミニウムを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させることで作製できる。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

2,001 - 2,015 / 2,015

[ Back to top ]