Fターム[5F110HK09]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | Si (2,015)

Fターム[5F110HK09]に分類される特許

81 - 100 / 2,015

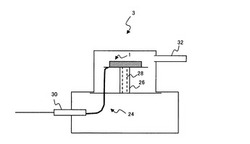

有機電界効果トランジスタ式ガスセンサおよび有機電界効果トランジスタ式ガスセンサの使用方法

【課題】ガスの検出感度とガスの脱離を両立することができる有機電界効果トランジスタ式ガスセンサおよびその使用方法を提供する。

【解決手段】有機半導体層を有する電界効果トランジスタ1と、電界効果トランジスタ1の温度を制御する温度制御機構24とを備える有機電界効果トランジスタ式ガスセンサ3である。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

π電子共役系化合物前駆体を用いた電子デバイス用インク組成物ならびにその用途

【課題】脱離反応時の前駆体膜の流動化を抑制すること。また、変換後の半導体材料の不連続化を低減すること。その結果として、特性の低下が抑えられ、ばらつきの抑えられた電気特性を得ることが可能な電子デバイス用インク組成物ならびにそれを用いた電子デバイス、電界効果トランジスタ、およびその製造方法を提供すること。

【解決手段】電子デバイス用インク組成物であって、高分子材料と、π電子共役系化合物前駆体と、前記高分子材料および前記前駆体を溶解させる溶媒を少なくとも含有することを特徴とするインク組成物。

(もっと読む)

液晶表示装置

【課題】横電界方式で液晶層を駆動する液晶表示装置において、その画像表示性能を向上させる。

【解決手段】画素領域のそれぞれには、ドレイン信号線DLに接続された薄膜トランジスタTFTと、複数のスリットを有し且つ透明導電膜で形成される第1の電極と、前記薄膜トランジスタと前記第1の電極を接続する接続領域を有し、透明導電膜で形成される平面状の第2の電極を有し、前記第2の電極は、前記第1の電極と前記第1の基板間に形成され、且つ、前記第1の電極とゲート信号線GLに重畳し、さらに、隣接する前記画素領域の第2の電極と接続されていることを特徴とする液晶表示装置である。

(もっと読む)

半導体装置及びその作製方法、ならびに電子機器

【課題】リーク電流が低減された半導体装置を提供すること。また、高い電界効果移動度と低いリーク電流が両立された半導体装置を提供すること。また、低消費電力化された電子機器を提供すること。また、マスク枚数を増やすことなくリーク電流を低減可能な、半導体装置の作製方法を提供すること。

【解決手段】高いキャリア移動度を有する半導体膜からなる半導体層の側面が、ソース電極及びドレイン電極と接しない構造とすればよい。また、フォトマスク数を増やすことなく、このような構成を有するトランジスタ構造を形成し、電子機器に適用すればよい。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オフ電流を抑えるための側壁酸化膜を有する表示装置と、その製造方法を提供することを目的とする。

【解決手段】

ゲート電極GTと、ゲート電極GTの上側に島状に形成される半導体層Sと、半導体層Sの側面に形成される側壁酸化膜OWと、半導体層Sの側方から延伸して半導体層Sの上側に形成されるドレイン電極DTおよびソース電極STと、を有する表示装置であって、側壁酸化膜OWは、2.1nm以上の厚みを有する、ことを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

基板洗浄装置、基板洗浄方法、表示装置の製造装置及び表示装置の製造方法

【課題】洗浄工程数を減らし、さらに、基板に対する汚染粒子の再付着を防止する。

【解決手段】基板洗浄装置1は、基板Wを搬送する搬送部2と、その搬送部2により搬送される基板Wの被洗浄面Sに、酸化膜除去可能な液体中に酸化性ガスを溶存状態および微小気泡状態で有する洗浄液を供給する供給ノズル3とを備え、その供給ノズル3は、被洗浄面S上に到達した微小気泡がサイズ変化を抑えつつ基板Wの外縁まで移動する流速で洗浄液を供給する。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

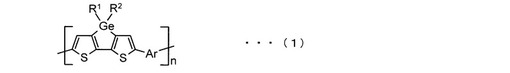

ジチエノゲルモール重合体及びそれを含有した有機半導体デバイス

【課題】耐久性及び半導体特性の安定性に優れた有機半導体材料として有用である熱安定性の高いジチエノゲルモール重合体、及びそれを含有する有機半導体材料より形成される有機半導体デバイスを提供する。

【解決手段】ジチエノゲルモール重合体は、下記化学式(1)

【化1】

(式中、R1及びR2はそれぞれ独立して置換基を有してもよい炭素数1〜20の炭化水素基であり、Arは置換基を有してもよい2価の芳香環と、芳香環数2〜7の置換基を有してもよい2価の多核芳香環と、置換基を有してもよい2価の芳香環及び/又は芳香環数2〜7の置換基を有してもよい2価の多核芳香環を複数連結させた2価のアリーレン基とから選ばれる何れかであり、nは少なくとも2の正数)で示されるものである。有機半導体デバイスは、このジチエノゲルモール重合体を有機半導体層とするものである。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

トランジスタ製造方法、トランジスタアレイ製造方法

【課題】トランジスタ上に物理的封じ込め手段を設けることなく高品質な印刷トランジスタを得る。

【解決手段】チャネル領域201を挟むよう基層(例えば220)上にコンタクトペア240、250を形成する。更に、チャネル領域201内で基層を覆う改質被覆221並びにコンタクトペアを覆う改質被覆241及び251のうち少なくとも何れかを形成する。改質被覆221、241及び251のうち少なくとも一部を含む受容面202上に半導体印刷液260’を堆積させ乾燥させることにより、チャネル領域201及びコンタクトペアの一部上に半導体活性領域を形成する。例えば改質被覆221の表面エネルギが改質被覆241、251の表面エネルギに比べて大きいか又は実質的に等しいという表面エネルギ分布が受容面に現れるよう、実現すべき表面エネルギ分布に応じて改質被覆221、241、251の素材等を選択してあるため、とぎれ等が生じることなく比較的厚みのある半導体活性領域を形成できる。

(もっと読む)

81 - 100 / 2,015

[ Back to top ]