Fターム[5F110HK09]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | Si (2,015)

Fターム[5F110HK09]に分類される特許

41 - 60 / 2,015

表示装置

【課題】フリンジフィールドスイッチングモードで駆動する液晶表示装置の作製方法において、フォトマスク数を削減することで製造工程の簡略化及び製造コストの削減をする。

【解決手段】透光性を有する絶縁基板上に第1の透明導電膜及び第1の金属膜を順に成膜し積層し、第1のフォトマスクである多階調マスクを用いて第1の透明導電膜及び第1の金属膜を形状加工し、絶縁膜、第1の半導体膜、第2の半導体膜、第2の金属膜を順に成膜し積層し、第2のフォトマスクである多階調マスクを用いて第2の金属膜、第2の半導体膜を形状加工し、保護膜を成膜し、第3のフォトマスクを用いて保護膜を形状加工し、第2の透明導電膜を成膜し、第4のフォトマスクを用いて第2の透明導電膜を形状加工する。

(もっと読む)

有機トランジスタ及びその製造方法

【課題】良好な電気的特性を有する有機トランジスタを製造するために有効な基準を明確にし、電気的特性に優れた有機トランジスタを提供する。

【解決手段】有機トランジスタ100は、絶縁基板1と、この絶縁基板1の上に所定のパターンで形成されたゲート電極3と、このゲート電極3を覆うように設けられたゲート絶縁層5と、このゲート絶縁層5に積層して設けられた有機半導体層7と、有機半導体層7の上に、部分的に形成された一対のソース電極9A及びドレイン電極9Bと、を備えている。有機トランジスタ100は、有機半導体層7との境界部分をなすゲート絶縁層5の上面5aの表面粗さRaが0.5nm以下である。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

非晶質半導体膜の評価方法、及び半導体装置の製造方法

【課題】フラットパネルディスプレイの高性能化に伴い、その製造工程でのアモルファスシリコン(a−Si)膜の評価・管理の必要性が高まってきた。

【解決手段】ガラス基板上にa−Si膜を成膜した試料32に対してレーザ光照射手段36からレーザ光を照射する。試料32におけるレーザ光を照射した各サンプリング点に、マイクロ波照射手段38からマイクロ波を照射し、反射波検出手段40でその反射強度を測定する。各サンプリング点での反射強度の測定結果に基づいて、基板面内でのa−Si膜の物性の均一性を評価する。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

(もっと読む)

半導体装置とその製造方法

【課題】微結晶シリコン膜を活性層とするTFTの閾値ドリフトを小さくする。

【解決手段】シリコンを含む半導体装置の製造方法であって、シリコンを含む原料ガスを水素ガスで600倍以上に希釈する工程と、前記希釈した原料ガスと水素ガスの混合ガスに高周波電力を加えて放電させる工程と、前記放電により分解した原料ガス中のシリコンを基板に堆積させる工程と、前記混合ガスの圧力を600Pa以上に制御する工程とを含み、前記原料ガスの水素ガスによる希釈率がD、前記混合ガスの圧力がP(Pa)のとき、前記高周波電力の電力密度Pw(W/cm2)をPw(W/cm2)×D(倍)/P(Pa)の値が0.083以上、かつ0.222以下となる範囲に設定することを特徴とする半導体装置の製造方法。

(もっと読む)

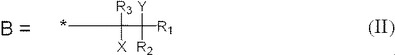

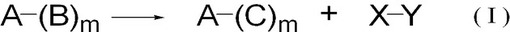

薄膜トランジスタ及びそれを用いた電子デバイス

【課題】特定構造のπ電子共役化合物前駆体を含む薄膜中の該前駆体のπ電子共役化合物への変換が、基板の耐熱温度に制限されることなく、且つ大気下で進行する、有機膜の製造方法。

【解決手段】π電子共役化合物前駆体A−(B)mを含む薄膜中の該前駆体A−(B)mが、活性エネルギー線の照射により、π電子共役系化合物A−(C)mと脱離性化合物X−Yに変換される。A−(B)m→A−(C)m+X−Y

(Aはπ電子共役系置換基、Bは溶媒可溶性置換基、mは自然数である。)

(もっと読む)

薄膜トランジスタ及びそれを用いた電子デバイス

【課題】優れた電気特性、大気安定性を有した薄膜トランジスタ及びそれを用いた電子デバイスをウェットプロセスにて作製するための、π電子共役系化合物前駆体、及びトランジスタ構造を提供する。

【解決手段】少なくとも下記一般式(I)で示される工程により得られる有機膜を用いたトップゲート型薄膜トランジスタ。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

【課題】バンク層の形成のために専用のマスクを用いたリソグラフィー工程が不要であり、製造工程を簡素化することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上にゲート電極12を形成した後、基体11及びゲート電極12上に絶縁層13を形成し、次いで、絶縁層13上に感光性絶縁材料から成るバンク層20を形成し、その後、基体側から、ゲート電極12を露光用マスクとして用いてバンク層20を露光し、ゲート電極12の上方のバンク層20を除去して、バンク層20に、ゲート電極の上方に位置する開口領域21を形成した後、塗布法に基づき、開口領域21内に半導体材料から成るチャネル形成領域14を形成し、その後、バンク層20上に一対のソース/ドレイン電極15を形成する各工程を備えている。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

積層体とその製造方法及びそれを用いたデバイス構造体の製造方法

【課題】各種デバイスを積層するための基材とするためのポリイミドフィルムと支持体との積層体であって、デバイス作製時の高温プロセスにおいても剥がれることなく、しかもポリイミドフィルム上にデバイスを作製した後には容易に支持体からポリイミドフィルムを剥離することができる積層体を提供する。

【解決手段】ポリイミドフィルム6として、少なくとも支持体1に対向させる面にプラズマ処理が施されたフィルムを用い、支持体1とポリイミドフィルム6とが対向する面の少なくとも一方にカップリング剤を用いて、接着剥離強度は異なり表面粗さは略同一である良好接着部分と易剥離部分とを形成するパターン化処理を施した後、重ね合わせて加圧加熱処理することとし、ポリイミドフィルム6は、70モル%以上がベンゾオキサゾール構造を有する芳香族ジアミン類を主成分とするジアミン類とテトラカルボン酸類との反応によって得られる。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制できる半導体装置を提供する。

【解決手段】ボトムゲート電極12aとトップゲート電極17aで半導体層14を挟むデュアルゲート型の薄膜トランジスタを有する半導体装置において、前記トップゲート電極は、第1のブラックマトリックス層によって形成され、前記半導体層は、前記トップゲート電極によって覆われている半導体装置である。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

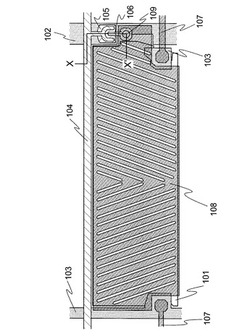

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層の幅を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制する。

【解決手段】ボトムゲート電極12aと第1のブラックマトリックス層17aで第1の半導体層14を挟むシングルゲート型の薄膜トランジスタを有する半導体装置であって、前記第1の半導体層と前記第1のブラックマトリックス層は重畳している半導体装置である。

(もっと読む)

半導体装置

【課題】電源をオフしてもデータを保持することができ、退避動作と復帰動作が不要なレジスタ回路を提供する。

【解決手段】複数のレジスタ構成回路と、オフ電流が小さい第1のトランジスタと、オフ電流が小さい第2のトランジスタと、を有するレジスタ回路において、データ保持部を前記第1のトランジスタのソース及びドレインの一方に接続し、前記第2のトランジスタのソース及びドレインの一方に接続する。前記第1のトランジスタ及び前記第2のトランジスタはオフ電流が小さいので、データ保持部の電荷がリークせず、レジスタ回路の電源をオフしてもデータ保持部にデータが保持される。そのため、退避動作と復帰動作を行わなくてよい。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

41 - 60 / 2,015

[ Back to top ]