Fターム[5F110HK09]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | Si (2,015)

Fターム[5F110HK09]に分類される特許

101 - 120 / 2,015

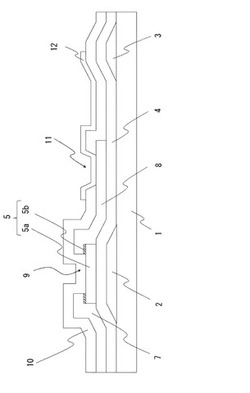

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

薄膜トランジスタ液晶ディスプレイのアレイ基板及びその製造方法

【課題】本発明はTFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】本発明はTFT−LCDアレイ基板及びその製造方法に関し、アレイ基板はベース基板と、ベース基板上に形成され画素領域を限定するゲートライン及びデータラインを含み、前記画素領域内には画素電極、薄膜トランジスタと共通電極が形成される。また、導電性薄膜材料により製造されるブラックマトリクスを含み、前記ブラックマトリクスは前記共通電極と接続される。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。また、本発明の目的は、基材がポリマー材料を有する半導体積層体を提供することである。

【解決手段】半導体積層体(110)を製造する本発明の方法は、(a)基材上にシリコン粒子分散体膜を形成する工程、(b)シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び(c)未焼結半導体シリコン膜に光を照射して、半導体シリコン膜を形成する工程を含む。また、本発明の半導体積層体(110)は、基材(112)及び半導体シリコン膜(118)を有し、基材が、ポリマー材料を有し、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である。

(もっと読む)

表示装置

【課題】光電変換素子を含む表示装置において、生産性および利便性に優れた表示装置を提供する。

【解決手段】複数の画素がマトリクス状に配列された表示部と、表示部に画像情報を伝送する駆動部と表示部に設けられ、且つレーザ光を検出する受光部と、受光部で検出するレーザ光の位置を解析し、位置に基づいて画像情報を操作し、操作に基づいた画像情報とは異なる画像情報を駆動部に伝送する情報処理部を有し、表示部の複数の画素はそれぞれ薄膜トランジスタを有し、受光部は複数の光電変換素子、走査回路、リセット回路および読み出し回路を有し、薄膜トランジスタおよび複数の光電変換素子は、同一の基板に設けられている表示装置である。

(もっと読む)

光電変換素子、光電変換回路及び表示装置

【課題】赤外光及び可視光に対する感度の高い光電変換素子を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆う第1のゲート絶縁層と、第1のゲート絶縁層上の結晶性半導体層と、結晶性半導体層上の非晶質半導体層と、非晶質半導体層上の不純物半導体層と、不純物半導体層に接するソース電極及びドレイン電極と、少なくともソース電極及びドレイン電極の間を覆う第2のゲート絶縁層と、第2のゲート絶縁層上の第2のゲート電極と、を有し、少なくともソース電極とドレイン電極の間に受光部が設けられ、第1のゲート電極は遮光性材料により結晶性半導体層及び非晶質半導体層のすべてと重畳し、第2のゲート電極は透光性材料により受光部と重畳し、第1のゲート電極は、ソース電極またはドレイン電極に電気的に接続されている光電変換素子を提供する。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

エッチング方法及び薄膜トランジスタの作製方法

【課題】アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差を大きくしたエッチング方法を提供する。

【解決手段】絶縁膜上に微結晶シリコン膜を形成し、前記微結晶シリコン膜上にアモルファスシリコン膜を形成し、前記アモルファスシリコン膜に1000Paより高圧力のH2とArの混合ガス雰囲気中でプラズマ処理を行うことにより前記微結晶シリコン膜を露出させてエッチングを行う。該エッチングは、アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差が大きい。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

表示素子の製造方法

【課題】安定した電流駆動能力を発揮させる。

【解決手段】アレイ基板20の製造方法は、基板上にゲート電極24aを形成するゲート電極形成工程と、ゲート電極24a上に不純物を含有するゲート絶縁膜24b、半導体膜SM、導電膜COの順で成膜する成膜工程と、導電膜CO上にレジストRSを塗布し、そのレジストRSに対してフォトマスクを介して露光を行った後に現像を行うことでレジストRSをパターニングするレジストパターニング工程と、パターニングされたレジストRSをマスクとして導電膜COをエッチングすることで開口領域OPを挟んで配されるソース電極24d及びドレイン電極24eを形成する導電膜パターニング工程と、開口領域OPから半導体膜SMを介してゲート絶縁膜24bに含有される不純物を脱離させる不純物脱離工程とを含む。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】半導体特性に影響を与えることなく、印刷法により形成される半導体の形状再現性に優れた電界効果型トランジスタの製造方法を提供すること。

【解決手段】基材上に、少なくともゲート電極、ソース電極、ドレイン電極と、半導体層およびゲート絶縁膜とが形成されてなる電界効果型トランジスタの製造方法であって、少なくともゲート絶縁膜上に半導体層を形成する工程を有し、該ゲート絶縁膜は露光によりシランカップリング剤と反応可能な官能基を生成し得る材料で形成されており、該工程の前に、ゲート絶縁膜上の半導体を形成する領域の周囲を露光する工程及び露光部においてフッ化アルキル基を有するシランカップリング剤と該官能基とを反応させる工程を有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

帯電体並びにそれを用いた電界効果トランジスタ及びメモリ素子

【課題】 フローティングゲートメモリやMNOSメモリのような極薄膜の絶縁層を必要とせず、印刷、塗布でメモリ素子が製造可能となる簡便で、注入電荷量の制御が容易な帯電体、並びにこの帯電体をゲート絶縁膜に用いてFETを作製することにより、閾値電圧制御が可能で、長時間制御された閾値電圧状態を保持可能なFET及びメモリ素子を提供する。

【解決手段】 電荷注入が生じる電界強度(以降、電荷注入耐圧)および絶縁耐圧がそれぞれECI,HおよびEBHである絶縁体(以下,高電荷注入耐圧材料)と、その電荷注入耐圧ECI,LがECI,L < ECl,Hの関係にある絶縁体(以下、低電荷注入耐圧材料)の二種類の絶縁体を積層した絶縁物で、高電荷注入耐圧材料と低電荷注入耐圧材料のそれぞれに接し離れた2枚の電極にECI,L < |E| < EBH の電界強度で電圧を印加して低電荷注入耐圧材料側から電荷を絶縁体内に注入して帯電させる帯電体。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】高い表示品質を実現することができるTFT、アクティブマトリクス基板及びそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2aと、ゲート電極2aを覆うように設けられたゲート絶縁膜3と、ゲート絶縁膜3の上に設けられ、ゲート電極の上方に配置された半導体膜5と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたソース電極7と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたドレイン電極9と、ソース電極7又はドレイン電極9の少なくとも一方とゲート絶縁膜3との間に設けられ、半導体膜5と分離して配置された低反射膜6と、を備え、低反射膜6が、平面視におけるゲート電極2aの外側において、ソース電極7、ドレイン電極9のパターンと略同一形状、又は、はみ出しているものである。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

101 - 120 / 2,015

[ Back to top ]