Fターム[5F110HK15]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | 半導体の結晶構造 (2,050) | 微結晶 (239)

Fターム[5F110HK15]に分類される特許

41 - 60 / 239

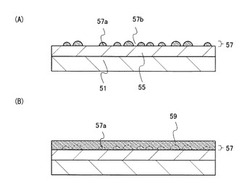

微結晶シリコン膜及びその作製方法、並びに半導体装置

【課題】結晶性の高い微結晶シリコン膜を作製する方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により第1の微結晶シリコン膜57をプラズマCVD法で形成し、第1の微結晶シリコン膜上に、第2の条件により第2の微結晶シリコン膜59を形成し、第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する第1の微結晶半導体膜を酸化絶縁膜上に形成した後、第2の条件により混相粒を結晶成長させて混相粒の隙間を埋めるように、第1の微結晶半導体膜上に第2の微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を50倍以上1000倍以下にして堆積性気体を希釈し、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を100倍以上2000倍以下にして堆積性気体を希釈し、処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

半導体装置の製造方法および表示パネルの製造方法

【課題】微結晶半導体膜を含むチャネル層の移動度を向上させる半導体装置の製造方法を提供する。

【解決手段】微結晶シリコン膜を堆積する工程と、水素プラズマ処理を施す工程を交互に複数回ずつ繰り返す。このような方法で微結晶シリコン膜を成膜すれば、微粒子内のマイクロクリスタル成分に含まれるシリコン原子の未結合手を終端したり、アモルファス成分を改質したりすることを、より効率的に行なうことができるので、TFTの移動度をより高めることができる。

(もっと読む)

半導体装置

【課題】電気特性が良好な半導体装置を提供する。または、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース配線及びドレイン配線として機能する配線との間に、微結晶シリコン膜及びシリコンカーバイド膜を有し、微結晶シリコン膜はゲート絶縁膜側に形成され、シリコンカーバイド膜は配線側に形成される。電気特性が良好な半導体装置を、生産性高く作製することができる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び発光装置

【課題】薄膜トランジスタのオン電流の向上を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタを製造する際に、チャネルが形成される半導体膜5b、6bとなる結晶性シリコンの半導体層9bを成膜する前処理として下地膜16にプラズマ処理を施すことによって、結晶化度を高めた半導体膜5b、6bを形成することができる。特に、プラズマ処理後に不純物半導体膜5g,5f(6g,6f)を形成するので、不純物半導体膜5g,5f(6g,6f)がプラズマに晒されて変質することがなく、薄膜トランジスタ5、6において、結晶性シリコンを含む半導体膜5b、6bに応じたオン電流の向上が得られる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 ソース/ドレイン電極と活性層との間に微結晶半導体からなるコンタクト層を設ける構成の薄膜トランジスタにおいて、直接堆積法によって形成されるコンタクト層の表面に凹凸ができ、凹部の膜厚が薄くなるためにオフリーク電流が生じ、電気特性が低下する。コンタクト層の凹部がオフリーク電流を抑制するのに必要な膜厚となるまで形成すると、コンタクト層表面の凹凸を活性層5で覆うことのできない部分が生じ、オン電流が流れる際の抵抗となる。

【解決手段】 コンタクト層4の凹部が、オフリーク電流を抑制するのに十分な膜厚になるまで形成した後、その表面を平坦化処理して活性層を形成する。これにより、コンタクト層4の表面を活性層5でほぼ均一に覆うことができ、オフリーク電流が低減され、オン電流の大きい特性のTFTを得ることができる。

(もっと読む)

半導体装置とその作製方法

【課題】薄膜トランジスタの閾値電圧を調整する。

【解決手段】薄膜トランジスタの作製に際して、処理室内に半導体材料ガスを導入し、ゲート電極を覆って設けられたゲート絶縁層上に前記処理室内で半導体膜を形成し、前記処理室内の前記半導体材料ガスを排気し、前記処理室内に希ガスを導入し、前記処理室内で前記半導体膜にプラズマ処理を行い、前記半導体膜上に不純物半導体膜を形成し、前記半導体膜と前記不純物半導体膜を島状に加工して半導体積層体を形成し、前記半導体積層体が有する不純物半導体層に接してソース電極及びドレイン電極を形成し、前記半導体膜の形成と前記希ガスプラズマ処理は、好ましくは前記処理室内の圧力及び温度を変化させずに行い、前記処理室内のガス種のみを異ならせる。希ガスとしてはアルゴンが好ましく、前記半導体膜には希ガス元素を2.5×1018cm−3以上含ませることが好ましい。

(もっと読む)

液晶表示装置及び電子機器

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製法を提供する。または、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】基板上に第1の微結晶半導体膜を形成した後、当該第1の微結晶半導体膜の表面を平坦化する処理を行い、次に、平坦化された第1の微結晶半導体膜の表面側の非晶質半導体領域を除去する処理を行って、結晶性が高く、且つ平坦性を有する第2の微結晶半導体膜を形成する。次に、第2の微結晶半導体膜上に第3の微結晶半導体膜を形成する。

(もっと読む)

発光装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつ

コストを抑えることができる発光装置の提案を課題とする。

【解決手段】画素部に発光素子と、発光素子への電流の供給を制御するTFTとを有する

画素が設けられており、駆動回路が有するTFTと、発光素子への電流の供給を制御する

TFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間

に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一

対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添

加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴と

する発光装置。

(もっと読む)

パターンの形成方法と当該パターンを備えた液晶表示装置の製造方法

【課題】透明膜を露光する際に、下地となる電極配線や露光ステージの溝等の存在により露光の光が局所的に強度が変動する反射光となってレジストを露光するため、高精細なパターニングができない。

【解決手段】透明膜上に遮光膜を形成する工程と、前記遮光膜上にレジスト層を塗布し、露光を行なってレジストパターンを形成する工程と、前記レジストパターンをマスクとして、前記遮光膜を除去する工程と、前記レジストパターンをマスクとして遮光膜を除去した後、透明膜を除去する工程と、前記レジストパターンを除去する工程と、前記レジストパターン除去後に、透明膜上の遮光膜を除去する工程を含むことを特徴とする。

(もっと読む)

表示装置およびその製造方法

【課題】 ボトムゲート構造のTFTを有する表示装置の生産性の低下を抑えるとともに、表示特性の劣化を抑える。

【解決手段】 複数の薄膜トランジスタが形成された基板を有する表示パネルを備え、前記薄膜トランジスタは、前記基板の上にゲート電極、ゲート絶縁膜、半導体膜の順に積層され、かつ、前記半導体膜の上にはソース電極の一部または全部およびドレイン電極の一部または全部がコンタクト膜を介して積層されており、前記コンタクト膜は、前記半導体膜と前記ソース電極との間に介在する部分および前記半導体膜と前記ドレイン電極との間に介在する部分を除いた部分が酸化されている表示装置であって、それぞれの前記コンタクト膜は、前記半導体膜と接している面の反対側が凹凸を有する曲面であり、かつ、最小膜厚が3nm以下、最大膜厚が4nm以上である表示装置。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な薄膜トランジスタを提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接し、且つ凹凸状の微結晶半導体領域及び非晶質半導体領域を有する半導体層と、半導体層の一部に接し、不純物半導体層と、不純物半導体層に接する配線と、微結晶半導体領域及び配線の間に形成される第1の酸化物領域と、非晶質半導体領域及び配線の間に形成される第2の酸化物領域とを有し、エネルギー分散型X線分光法において測定される、配線を構成する元素のプロファイル及び半導体層を構成する元素のプロファイルの交点から、半導体層側において、第1の酸化物領域における酸素プロファイルの最大傾き接線m1及び第2の酸化物領域における酸素プロファイルの最大傾き接線m2は、1<m1/m2<10である薄膜トランジスタである。

(もっと読む)

TFT−LCDアレー基板及びその製造方法

【課題】TFT−LCDアレー基板及びその製造方法を提供する。

【解決手段】TFT−LCDアレー基板の製造方法は、基板にゲートライン及びそのゲートラインと接続するゲート電極を形成し、前記ゲート電極にゲート絶縁層と半導体層とを形成し、前記半導体層にオーム接触層を形成することにより、基板にトランジスタ部を形成する工程と、前記工程で作製された基板に、ゲートラインとゲート電極と電気的に絶縁し、オーム接触層を介して前記半導体層の両側にオーム接触する透明画素電極層とソース・ドレイン電極金属層と順次堆積する工程と、作製された基板に、グレートーンマスクでマスキング及びエッチングを行うことにより、透明画素電極及びソース・ドレイン電極が同時に形成する工程とを含む。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層に接する配線とを有し、半導体層において、ゲート絶縁層側に形成される凹凸状の微結晶半導体領域と、当該微結晶半導体領域に接する分離された非晶質半導体領域とを有し、微結晶半導体領域は、非晶質半導体領域に覆われていない第1の微結晶半導体領域と、分離された非晶質半導体領域と接する第2の微結晶半導体領域とで形成され、第1の微結晶半導体領域の厚さd1は第2の微結晶半導体領域の厚さd2より薄く、且つ第1の微結晶半導体領域の厚さd1が30nm以上である。

(もっと読む)

薄膜トランジスタとその作製方法

【課題】ドレイン電流のオン/オフ比が高く維持されつつ、光電流とオフ電流が十分に小さい薄膜トランジスタを提供することを課題とする。

【解決手段】ゲート電極層と、ゲート電極層を覆って設けられたゲート絶縁層と、ゲート電極層と全面が重畳して設けられた第1の半導体層と、第1の半導体層上に接して設けられ、前記第1の半導体層よりもキャリア移動度が低い第2の半導体層と、第2の半導体層に接して設けられた不純物半導体層と、少なくとも前記第1の半導体層の側壁を覆って設けられたサイドウォール絶縁層と、少なくとも前記不純物半導体層に接して設けられたソース電極及びドレイン電極層と、を有する薄膜トランジスタとする。第2の半導体層は、第1の半導体層上に離間して設けられていてもよい。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好で生産性の高い薄膜トランジスタを提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層に接する配線とを有し、半導体層において、ゲート絶縁層側に形成される凹凸状の微結晶半導体領域と、当該微結晶半導体領域に接する非晶質半導体領域とを有し、半導体層及び配線の間に障壁領域を有する薄膜トランジスタである。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】駆動回路及び画素部を有し、駆動回路は、デュアルゲート型の薄膜トランジスタを用いて構成され、画素部はシングルゲート型の薄膜トランジスタを用いて構成される表示装置である。該表示装置おけるデュアルゲート型の薄膜トランジスタは、半導体層が微結晶半導体領域及び一対の非晶質半導体領域で形成され、ゲート絶縁層及び絶縁層が半導体層の微結晶半導体領域に接する。

(もっと読む)

半導体装置、表示装置、液晶テレビジョン装置、及びELテレビジョン装置

【課題】より良好な電気的特性を有する化合物半導体を用いた薄膜トランジスタを有する

半導体装置、及びその作製方法を提供することを目的とする。

【解決手段】半導体層として化合物半導体材料を用い、半導体層とソース電極層及びドレ

イン電極層との間に、それぞれ導電性の有機化合物及び無機化合物を含むバッファ層を形

成する。バッファ層は有機化合物及び無機化合物を含む層として形成される。化合物半導

体材料を用いた半導体層とソース電極層及びドレイン電極層との間に介在するバッファ層

によって、半導体層とソース電極層及びドレイン電極層との導電性は向上し、電気的に良

好な接続を行うことができる。

(もっと読む)

半導体膜の製造方法および薄膜トランジスタの製造方法

【課題】大面積の基板上に低コストで微結晶性の半導体膜を形成することが可能な半導体膜の製造方法および薄膜トランジスタの製造方法を提供する。

【解決手段】一次微結晶半導体膜11に対して成膜成分を有しないプラズマ処理を行うことにより、一次微結晶半導体膜11の一部をエッチングして薄膜化微結晶半導体膜12を形成し、この薄膜化微結晶半導体膜12から二次微結晶半導体膜13を形成する。一次微結晶半導体膜11のエッチングにより結晶性を乱す要因となっている部分が選択的に除去され、結晶性の良い薄膜化微結晶半導体膜12となる。二次微結晶半導体膜13は、薄膜化微結晶半導体膜12の良好な結晶性を引き継いで成長し、基材10との界面においてもアモルファス相が少なくなる。二次微結晶半導体膜13を形成する前に、薄膜化微結晶半導体膜12を、固相成長を起こす温度でアニール処理し、更に結晶性を高めてもよい。

(もっと読む)

41 - 60 / 239

[ Back to top ]