Fターム[5F110HK35]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011) | プラズマCVD (871)

Fターム[5F110HK35]の下位に属するFターム

ECRプラズマCVD (4)

Fターム[5F110HK35]に分類される特許

101 - 120 / 867

薄膜トランジスタ液晶ディスプレイのアレイ基板及びその製造方法

【課題】本発明はTFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】本発明はTFT−LCDアレイ基板及びその製造方法に関し、アレイ基板はベース基板と、ベース基板上に形成され画素領域を限定するゲートライン及びデータラインを含み、前記画素領域内には画素電極、薄膜トランジスタと共通電極が形成される。また、導電性薄膜材料により製造されるブラックマトリクスを含み、前記ブラックマトリクスは前記共通電極と接続される。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

表示装置

【課題】光電変換素子を含む表示装置において、生産性および利便性に優れた表示装置を提供する。

【解決手段】複数の画素がマトリクス状に配列された表示部と、表示部に画像情報を伝送する駆動部と表示部に設けられ、且つレーザ光を検出する受光部と、受光部で検出するレーザ光の位置を解析し、位置に基づいて画像情報を操作し、操作に基づいた画像情報とは異なる画像情報を駆動部に伝送する情報処理部を有し、表示部の複数の画素はそれぞれ薄膜トランジスタを有し、受光部は複数の光電変換素子、走査回路、リセット回路および読み出し回路を有し、薄膜トランジスタおよび複数の光電変換素子は、同一の基板に設けられている表示装置である。

(もっと読む)

光電変換素子、光電変換回路及び表示装置

【課題】赤外光及び可視光に対する感度の高い光電変換素子を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆う第1のゲート絶縁層と、第1のゲート絶縁層上の結晶性半導体層と、結晶性半導体層上の非晶質半導体層と、非晶質半導体層上の不純物半導体層と、不純物半導体層に接するソース電極及びドレイン電極と、少なくともソース電極及びドレイン電極の間を覆う第2のゲート絶縁層と、第2のゲート絶縁層上の第2のゲート電極と、を有し、少なくともソース電極とドレイン電極の間に受光部が設けられ、第1のゲート電極は遮光性材料により結晶性半導体層及び非晶質半導体層のすべてと重畳し、第2のゲート電極は透光性材料により受光部と重畳し、第1のゲート電極は、ソース電極またはドレイン電極に電気的に接続されている光電変換素子を提供する。

(もっと読む)

エッチング方法及び薄膜トランジスタの作製方法

【課題】アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差を大きくしたエッチング方法を提供する。

【解決手段】絶縁膜上に微結晶シリコン膜を形成し、前記微結晶シリコン膜上にアモルファスシリコン膜を形成し、前記アモルファスシリコン膜に1000Paより高圧力のH2とArの混合ガス雰囲気中でプラズマ処理を行うことにより前記微結晶シリコン膜を露出させてエッチングを行う。該エッチングは、アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差が大きい。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

薄膜トランジスタ

【課題】 結晶性に優れ、電気特性、特にリーク電流の少ない結晶性シリコン薄膜半導体装置を提供する。

【解決手段】 ソース電極およびドレイン電極上に非晶質シリコン層を形成し、その上に微結晶シリコン層、ゲート絶縁層、ゲート電極を形成する薄膜トランジスタであって、前記非晶質シリコン層と前記ソース電極とドレイン電極とが前記微結晶シリコン層を介して接続する領域と、前記非晶質シリコン層と前記ソース電極およびドレイン電極と直接接続する領域と、を有する。

(もっと読む)

結晶性半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性半導体の核生成を均一にする。

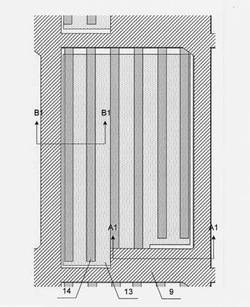

【解決手段】ガス管から導入された成膜ガスを拡散する第2のガス拡散室と、前記第2のガス拡散室と分散板を隔てて設けられ、該分散板のガス孔から成膜ガスが導入される第1のガス拡散室と、を介して、前記第1のガス拡散室とシャワー板を隔てて設けられた処理室内に該シャワー板のガス孔から成膜ガスを供給し、前記成膜ガスを導入することによって前記処理室内の圧力を2000Pa以上100000Pa以下とし、前記処理室内に電界を生じさせる一対の電極のうち、一方の電極面から電界強度が均一な高周波電力を供給することでグロー放電プラズマを生成させ、前記対向する電極の他方に配された基板上に結晶核を生じさせ、その後、該結晶核を成長させて結晶性半導体膜を作製する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】高性能な電気特性を実現しうるpoly−Si膜の結晶性分布を有した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、絶縁性の基板と、前記絶縁性基板の上に形成されたゲート電極と、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜の上に形成された結晶シリコン膜と、前記結晶シリコン膜の端部の上方に形成されたソース電極と、前記結晶シリコン膜における前記ソース電極が形成された端部と対向する端部の上方に形成され、前記ソース電極と離間しているドレイン電極とを具備する薄膜トランジスタにおいて、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されている前記結晶シリコン膜の端部から、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されていない前記結晶シリコン膜の中央部に向かって、前記結晶シリコン膜の結晶化率が小さくなっている。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】電気的特性が良好な半導体装置の作製方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、HBrガスと、CF4ガスと、酸素ガスの混合ガスを含むガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを薄膜トランジスタのバックチャネル部を形成するエッチングに適用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。

(もっと読む)

アレイ基板及び液晶ディスプレイ

【課題】本発明はアレイ基板及び液晶ディスプレイに関する。

【解決手段】本発明は、アレイ基板と液晶ディスプレイを開示している。このアレイ基板は、サブストレートと、前記サブストレートに形成された、横縦方向に交差して複数の画素ユニットを囲んで形成したデータライン及びゲートラインと、を備え、各画素ユニットは画素電極と薄膜トランジスタースイッチ素子とを備え、前記薄膜トランジスタースイッチ素子は、ゲート電極、ソース電極、ドレイン電極、活性層を備え、前記ゲート電極と活性層との間にゲート絶縁層が設けられ、前記ゲート絶縁層は不透明絶縁層を含む。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

薄膜素子の作製方法及び半導体装置の作製方法

【課題】所定の層が水分などに一切曝されることない半導体装置の作製方法を提供することを課題とする。

【解決手段】第1の膜、第2の膜及び第3の膜をこの順に積層して形成し、第3の膜上にレジストマスクを形成し、レジストマスクを用いて第3の膜をエッチングすることでマスク層を形成し、レジストマスクを薬液により除去し、マスク層を用いて第2の膜と第1の膜をドライエッチングすることで、第2の層と第1の層を形成し、少なくとも第2の層と第1の層を覆って第4の膜を形成し、第4の膜をエッチバックすることで、少なくとも第1の層の側面のすべてを覆ってサイドウォール層を形成することで薄膜素子を作製する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

トランジスタの作製方法

【課題】特性のバラツキが少なく、電気特性が良好なトランジスタを作製する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体を含む半導体層を形成し、半導体層上に不純物半導体層を形成し、不純物半導体層上にマスクを形成した後、マスクを用いて半導体層及び不純物半導体層をエッチングして、半導体積層体を形成し、マスクを除去した後に半導体積層体を希ガスを含む雰囲気で発生させたプラズマに曝して半導体積層体の側面に障壁領域を形成し、半導体積層体の不純物半導体層に接する配線を形成する。

(もっと読む)

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

101 - 120 / 867

[ Back to top ]