Fターム[5F110HK35]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011) | プラズマCVD (871)

Fターム[5F110HK35]の下位に属するFターム

ECRプラズマCVD (4)

Fターム[5F110HK35]に分類される特許

121 - 140 / 867

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

半導体装置、パワーダイオード及び整流器

【課題】高耐圧、低逆方向飽和電流、高いオン電流などの電気特性を有する半導体装置を提供することである。なかでも、非線形素子より構成されるパワーダイオード及び整流器を提供することである。

【解決手段】第1の電極と、第1の電極を覆うゲート絶縁層と、ゲート絶縁層と接して且つ第1の電極と重畳する酸化物半導体層と、酸化物半導体層の端部を覆う一対の第2の電極と、一対の第2の電極及び酸化物半導体層を覆う絶縁層と、絶縁層に接して且つ一対の第2の電極の間に設けられる第3の電極と、を有し、一対の第2の電極は酸化物半導体層の端面に接する半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

薄膜トランジスタ

【課題】電気特性の変動が少なく、信頼性の高いトランジスタを提供する。また、電気特性の変動が少なく、信頼性の高いトランジスタを、生産性高く作製する。また、経年変化の少ない表示装置を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース領域及びドレイン領域として機能する不純物半導体膜との間に、微結晶半導体領域及び一対の非晶質半導体領域を有する半導体積層体を有し、微結晶半導体領域は、ゲート絶縁膜側の窒素濃度が少なく、非晶質半導体に接する領域の窒素濃度が高く、且つ非晶質半導体との界面が凹凸状である。

(もっと読む)

薄膜トランジスタおよび画像表示装置

【課題】ホールの多数発生を抑制し、かつリーク電流の増大を抑制することができる薄膜トランジスタを提供する。

【解決手段】本発明に係る薄膜トランジスタでは、半導体層12は、平面視において、ゲート電極2の端辺部2A,2Bからソース電極7およびドレイン電極8が引き出された部分において、ゲート電極2から外側に延在する延在部P1,P2,P3を有している。また、平面視において、ソース電極7とゲート電極2の端辺部2A,2Bとが交差する部分L1,L2は、チャネル形成領域13に接するソース電極7の部分LSと、チャネル長方向Yにおいて重ならない。さらに、平面視において、ドレイン電極8とゲート電極2の端辺部2Bとが交差する部分L3は、チャネル形成領域13に接するドレイン電極8の部分LDと、チャネル長方向Yにおいて重ならない。

(もっと読む)

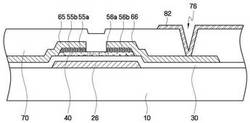

液晶表示装置

【課題】画素内におけるTFTのON電流を増大させ、かつ、ON電流のばらつきを抑える。

【解決手段】TFTにおける半導体層103と1層目のn+a−Si層14をプラズマCVDによって連続して形成する。半導体層103と1層目のn+a−Si層104を同時にパターニングする。その後、2層目のn+a−Si層105を1層目のn+a−Si層104の上と、半導体層103の側部を覆うように形成する。半導体層103の上に連続して1層目のn+a−Si層104を形成することによってTFTのON電流を増大させることが出来るとともに、ON電流のばらつきを小さくすることが出来る。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】デュアルゲート型トランジスタのゲートと、ソースまたはドレインの間の寄生容量を低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第3の導電層は、第1の半導体層の第2の半導体層と重畳していない部分と重畳し、且つ第2の導電層の一部とも重畳している構造とする。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】透明導電膜にピンホール等の欠陥が生じたとしても金属導電膜の腐食を抑制し、透明導電膜と金属導電膜との間の導通を確実にとることが可能な薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】金属導電膜としてのゲート端子121、ドレイン端子122上にOC−SiN膜109を形成し、ゲート端子121及びドレイン端子122が露出するようにコンタクトホールを形成し、コンタクトホールを介してゲート端子121及びドレイン端子122に接触するようにITO膜を成膜してパターニングし、ITO膜に対して酸化膜形成処理を行う。これにより、ITO膜にピンホール等の欠陥が発生していた場合には、欠陥を介してITO膜下のゲート端子121ドレイン端子122の一部が酸化されて酸化膜が形成される。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】レジストの広がりを容易に制御して、寄生容量の増加を抑制する。

【解決手段】ゲート電極11aa上に、ゲート絶縁膜12、第1半導体膜13、第2半導体膜14及び金属膜を成膜し、金属膜上にレジストを形成する工程と、レジストから露出する金属膜、及びレジストの薄膜部の下層に配置する金属膜の上層部をエッチングしてソースドレイン形成層15aを形成する工程と、レジストRbbから露出するソースドレイン形成層15a及び第2半導体膜14の温度差に基づいてリフロー処理を行いレジストRbcに変形する工程と、レジストRbcを用いて第1半導体層13a及び第2半導体層形成層14aを形成する工程と、レジストRbcを除去した後に、ソース電極及びドレイン電極を形成し、両電極から露出する第2半導体層形成層14aをエッチングして第2半導体層14bを形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びにその薄膜トランジスタを備えた装置

【課題】低温で作製可能であり、高い電界効果移動度を示す薄膜トランジスタを提供する。

【解決手段】酸化物半導体層からなる活性層を備えた薄膜トランジスタにおいて、活性層が、ゲート電極側から膜厚方向に第1の電子親和力χ1を有する第1の領域A1、第1の電子親和力χ1よりも小さい第2の電子親和力χ2を有する第2の領域A2とを含み、第1の領域A1を井戸層、第2の領域A2とゲート絶縁膜とを障壁層とする井戸型ポテンシャルを構成するものとする。ここで、活性層を、a(In2O3)・b(Ga2O3)・c(ZnO)から成る酸化物半導体層からなるものとし、第2の領域A2のb/(a+b)を第1の領域A1のb/(a+b)よりも大きくする。

(もっと読む)

微結晶シリコン膜の作製方法および薄膜トランジスタの作製方法

【課題】絶縁膜と微結晶シリコン膜との密着性を向上させた微結晶シリコン膜の作製方法を提供する。

【解決手段】絶縁膜55上に、後のプラズマ酸化等により完全に酸化される高さ(例えば0nmより大きく5nm以下)の微結晶シリコン粒、または後のプラズマ酸化等により完全に酸化される膜厚(例えば0nmより大きく5nm以下)の微結晶シリコン膜もしくはアモルファスシリコン膜を形成し、前記微結晶シリコン粒または前記微結晶シリコン膜もしくはアモルファスシリコン膜に酸素を含むプラズマ処理またはプラズマ酸化を施すことにより、前記絶縁膜上に酸化シリコン粒57aまたは酸化シリコン膜を形成し、前記酸化シリコン粒または前記酸化シリコン膜の上に微結晶シリコン膜59を形成する微結晶シリコン膜の作製方法である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】微結晶シリコンを備える薄膜トランジスタにおいて、光リーク電流、及び、電界起因のリーク電流を抑制することが可能な技術を提供することを目的とする。

【解決手段】薄膜トランジスタは、ゲート電極2上にゲート絶縁膜6を介して順に形成された微結晶シリコン膜8、非晶質シリコン膜9、及び、N型非晶質シリコン膜10を含む半導体層25と、微結晶シリコン膜8の端部8bと接触し、かつ、N型非晶質シリコン膜10と接続されたドレイン電極12とを備える。半導体層25は、平面視においてゲート電極2の外周よりも内側に形成され、微結晶シリコン膜8の端部8bは、N型非晶質シリコン膜10と同じN型の導電型を有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

121 - 140 / 867

[ Back to top ]