Fターム[5F110HK35]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011) | プラズマCVD (871)

Fターム[5F110HK35]の下位に属するFターム

ECRプラズマCVD (4)

Fターム[5F110HK35]に分類される特許

81 - 100 / 867

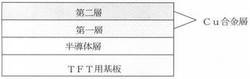

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、センサ及びX線デジタル撮影装置

【課題】基板の選択性を広げつつ、電界効果移動度が高くノーマリーオフ駆動する薄膜トランジスタ等を得る。

【解決手段】活性層の成膜工程での成膜室中の雰囲気の全圧に対する酸素分圧をPo2depo(%)とし、熱処理工程中の雰囲気の全圧に対する酸素分圧をPo2anneal(%)としたときに、熱処理工程時の酸素分圧Po2anneal(%)が、−20/3Po2depo+40/3≦Po2anneal≦−800/43Po2depo+5900/43の関係を満たすように成膜工程と熱処理工程とを行う。

(もっと読む)

半導体装置及びその作製方法、ならびに電子機器

【課題】リーク電流が低減された半導体装置を提供すること。また、高い電界効果移動度と低いリーク電流が両立された半導体装置を提供すること。また、低消費電力化された電子機器を提供すること。また、マスク枚数を増やすことなくリーク電流を低減可能な、半導体装置の作製方法を提供すること。

【解決手段】高いキャリア移動度を有する半導体膜からなる半導体層の側面が、ソース電極及びドレイン電極と接しない構造とすればよい。また、フォトマスク数を増やすことなく、このような構成を有するトランジスタ構造を形成し、電子機器に適用すればよい。

(もっと読む)

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

酸化物半導体薄膜の製造方法、電界効果型トランジスタ、表示装置及びセンサ

【課題】SGZO系酸化物半導体薄膜において、低温アニールによる低抵抗化が起こらず、成膜時の抵抗値と低温アニール後の抵抗値が同等となる組成を明らかとし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した製造方法を提供する。

【解決手段】構成元素の組成比をSn:Ga:Zn=a:b:cとした場合、組成比が、a+b=2、且つ1≦a≦2、且つ1≦c≦11/2、且つc≧−7b/4+11/4を満たす酸化物半導体薄膜を基板上に成膜する成膜工程と、成膜工程後、酸化性雰囲気中で100℃以上300℃未満の熱処理を施す熱処理工程と、を有する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オフ電流を抑えるための側壁酸化膜を有する表示装置と、その製造方法を提供することを目的とする。

【解決手段】

ゲート電極GTと、ゲート電極GTの上側に島状に形成される半導体層Sと、半導体層Sの側面に形成される側壁酸化膜OWと、半導体層Sの側方から延伸して半導体層Sの上側に形成されるドレイン電極DTおよびソース電極STと、を有する表示装置であって、側壁酸化膜OWは、2.1nm以上の厚みを有する、ことを特徴とする表示装置。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

基板洗浄装置、基板洗浄方法、表示装置の製造装置及び表示装置の製造方法

【課題】洗浄工程数を減らし、さらに、基板に対する汚染粒子の再付着を防止する。

【解決手段】基板洗浄装置1は、基板Wを搬送する搬送部2と、その搬送部2により搬送される基板Wの被洗浄面Sに、酸化膜除去可能な液体中に酸化性ガスを溶存状態および微小気泡状態で有する洗浄液を供給する供給ノズル3とを備え、その供給ノズル3は、被洗浄面S上に到達した微小気泡がサイズ変化を抑えつつ基板Wの外縁まで移動する流速で洗浄液を供給する。

(もっと読む)

電子素子及びその製造方法

【課題】素子性能の低下が抑制される電子素子を提供する。

【解決手段】基板12と、前記基板上の動作領域に配置された第1導電層14Gと、前記第1導電層上に該第1導電層と接して配置された絶縁層16と、前記基板上の非動作領域で前記絶縁層下に該絶縁層と接して配置され、前記絶縁層の亀裂30の発生を誘導する亀裂誘導部であって、前記第1導電層上の前記絶縁層よりも該亀裂誘導部上の前記絶縁層に亀裂を優先的に発生させる亀裂誘導部22と、を有する電子素子10。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

酸化物半導体素子及び半導体装置

【課題】半導体層に結晶性を有する酸化物半導体を用いた、移動度の高い酸化物半導体素子を提供する。

【解決手段】第1の酸化物半導体膜及び、第1の酸化物半導体膜に接して第1の酸化物半導体膜よりバンドギャップが大きい第2の酸化物半導体膜の積層構造を有する層を酸化物半導体層として用いた。これにより、チャネル領域は、第2の酸化物半導体膜と接する第1の酸化物半導体膜の界面近傍(つまり、バンドギャップが小さい酸化物半導体膜の界面近傍)に形成される。また、第1の酸化物半導体膜と第2の酸化物半導体膜の界面は、お互いの未結合手が結合し合っている。このため、第2の酸化物半導体膜と接する第1の酸化物半導体膜の界面近傍に形成されるチャネル領域では、未結合手による電子トラップなどに起因した移動度の低下を低減できる。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】支持基板上に絶縁層を形成し、当該絶縁層上に高純度化された酸化物半導体と、SOI(Silicon On Insulator)基板である単結晶シリコンを用いて半導体装置を構成する。高純度化された酸化物半導体を用いて構成したトランジスタは、リーク電流が極めて小さいため、長期間にわたって情報を保持することが可能である。また、SOI基板を用いることにより、絶縁層上に形成された薄い単結晶シリコンの特長を生かすことで、トランジスタを完全空乏型とすることができるため、高集積、高速駆動、低消費電力など付加価値の高い半導体集積回路が実現できる。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

81 - 100 / 867

[ Back to top ]