Fターム[5F110HK35]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011) | プラズマCVD (871)

Fターム[5F110HK35]の下位に属するFターム

ECRプラズマCVD (4)

Fターム[5F110HK35]に分類される特許

161 - 180 / 867

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置

【課題】生産性の高い半導体材料を用い、且つ耐圧性を向上させたトランジスタを提供することを課題の一とする。または、高耐圧のトランジスタを用いた大電力向けの半導体装置を提供することを課題の一とする。

【解決手段】トランジスタにおいて、高電界の印加されるドレイン電極を平坦な面上に形成し、且つ、ゲート電極の、チャネル幅方向のドレイン電極側の端部、およびチャネル長方向の端部を、ゲート絶縁層を介して酸化物半導体層で覆うことによって、トランジスタの耐圧を向上させる。また、該トランジスタを用いた大電力向けの半導体装置を提供することができる。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

微結晶シリコン膜及びその作製方法、並びに半導体装置

【課題】結晶性の高い微結晶シリコン膜を作製する方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により第1の微結晶シリコン膜57をプラズマCVD法で形成し、第1の微結晶シリコン膜上に、第2の条件により第2の微結晶シリコン膜59を形成し、第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、疎水化処理を要することなく、フォトリソグラフィー技術による酸化シリコン膜のパターニングが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、基板上に形成された酸化シリコン膜上に機能層を形成する機能層形成工程と、上記機能層上に第1フォトレジストを塗布し、フォトリソグラフィー法により上記機能層および上記酸化シリコン膜をパターニングし、上記第1フォトレジストを除去する第1パターニング工程と、パターニングされた上記機能層上に第2フォトレジストを塗布し、フォトリソグラフィー法により上記機能層をさらにパターニングし、上記第2フォトレジストを除去する第2パターニング工程とを有し、上記機能層と上記第1フォトレジストおよび上記第2フォトレジストとの接触角が20度以下であることを特徴とする半導体素子の製造方法を提供する。

(もっと読む)

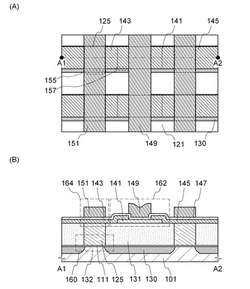

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する第1の微結晶半導体膜を酸化絶縁膜上に形成した後、第2の条件により混相粒を結晶成長させて混相粒の隙間を埋めるように、第1の微結晶半導体膜上に第2の微結晶半導体膜を積層形成する。第1の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を50倍以上1000倍以下にして堆積性気体を希釈し、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、シリコンまたはゲルマニウムを含む堆積性気体の流量に対する水素の流量比を100倍以上2000倍以下にして堆積性気体を希釈し、処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】IGZO系電界効果型薄膜トランジスタにおいて、消費電力が少なく、環境変化及び駆動に対する素子安定性の優れたものとする

【解決手段】電界効果型トランジスタ1aは、基板10上に、ゲート電極21と、ゲート絶縁膜30と、IGZO系アモルファス酸化物からなる(不可避不純物を含んでもよい)活性層40と、活性層40上にパターン形成されてなるソース電極22及びドレイン電極23と、酸化ガリウムを主成分とする第1の保護層50とを備え、保護層50は、少なくとも、ソース電極22とドレイン電極23との間のバックチャネル領域の活性層40上に形成されてなるものである。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】信頼性および再現性が優れるとともに、歩留まりが高く生産性が優れた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極を形成する工程と、ゲート電極を覆って基板上に第1の絶縁膜を形成し、第1の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第2の絶縁膜を形成して、第1の絶縁膜、酸化物半導体膜および第2の絶縁膜からなる積層体を得る工程と、積層体の第1の絶縁膜、酸化物半導体膜および第2の絶縁膜をパターニングして、それぞれゲート絶縁層、活性層およびチャネル保護層を形成する工程と、ソース電極およびドレイン電極を形成する工程とを有する。第1の絶縁膜、酸化物半導体膜および第2の絶縁膜は、大気に曝されることなく連続して形成される。

(もっと読む)

薄膜トランジスタの製造方法

【課題】オーミックコンタクト層の膜厚やドライエッチング時のエッチングレートに依存せず所望のエッチングが可能となる薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性基板上に、ゲート電極と、ゲート電極を覆うように形成されたゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、を備える薄膜トランジスタの製造方法であって、絶縁性基板上に、ゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、がこの順に積層される積層ステップと、積層ステップによって積層されたソース・ドレイン電極とオーミックコンタクト層とがエッチングガスでエッチングされるエッチングステップと、オーミックコンタクト層がエッチングされてゲート絶縁膜が露出し始める点をエッチング終了ポイントとして検知するエッチング終了検知ステップと、を備える薄膜トランジスタの製造方法。

(もっと読む)

電子デバイスの製造方法、薄膜トランジスタ、電気光学装置及びセンサー

【課題】簡便に界面の欠陥を低減することを可能とする。

【解決手段】大気と遮断された真空成膜室内で、基板上に酸素不定比性のある酸化物を含有する第1層を成膜する第1成膜工程と、前記第1層上に前記第1層と同一材料又は異なる材料からなる第2層を成膜する第2成膜工程と、前記第1成膜工程後前記第2成膜工程前までの間、前記第1層を、前記真空成膜室を含む大気と遮断された室内で、前記第1成膜工程における前記真空成膜室内の酸素分圧よりも高い酸素分圧下に保持する分圧制御工程と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

薄膜トランジスタの製造方法、並びに、薄膜トランジスタ、イメージセンサー、X線センサー及びX線デジタル撮影装置

【課題】酸化物半導体層を有する薄膜トランジスタを製造する際に熱処理による電気特性のバラツキが抑制され、特に大面積のデバイスの作製に適した薄膜トランジスタの製造方法を提供する。

【解決手段】基板11上に、酸化物半導体層12と、ソース電極13と、ドレイン電極14と、ゲート絶縁膜15と、ゲート電極とを有する薄膜トランジスタを製造する方法であって、隣接する層の組成が異なる3層以上の積層構造を有し、かつ、ゲート電極に最も近い側に配置された層12Cとゲート電極から最も遠い側に配置された層12Aとの間に、ゲート電極に最も近い側に配置された層及びゲート電極から最も遠い側に配置された層よりも比抵抗が小さい低抵抗層12Cが少なくとも1層存在する酸化物半導体層を形成する工程と、前記酸化物半導体層を形成した後、熱処理する工程と、を含む薄膜トランジスタ1の製造方法。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

薄膜トランジスタとその製造方法、アクティブマトリックス基板、及び電気光学装置

【課題】製造効率が良く、かつ、光リーク電流の発生が抑制されたTFTを提供する。

【解決手段】TFT101は、ゲート電極2が、基板1側から見て、第1の金属遮光膜Aと絶縁膜Bと第1の金属遮光膜Aよりも形成面積の小さい第2の金属遮光膜Cとの積層構造を有し、第1の金属遮光膜Aと第2の金属遮光膜Cのうち一方がゲート回路に電気的に接続され、他方がゲート回路から絶縁された構造を有するものであり、第1の金属遮光膜Aは、半導体積層膜10の形成領域を含む領域に形成されており、チャネル層8において、少なくともソース電極11とドレイン電極12との間の領域13は、第1の金属遮光膜Aと第2の金属遮光膜Cのうちゲート回路に電気的に接続された金属遮光膜と近接し、チャネル層8の両端部は、ゲート回路から絶縁された金属遮光膜と近接するよう、第1の金属遮光膜A及び第2の金属遮光膜Cが形成されたものである。

(もっと読む)

成膜方法及び半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供することを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でスパッタリングを行う。

(もっと読む)

161 - 180 / 867

[ Back to top ]