Fターム[5F110HL05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | シリサイド (187)

Fターム[5F110HL05]に分類される特許

41 - 60 / 187

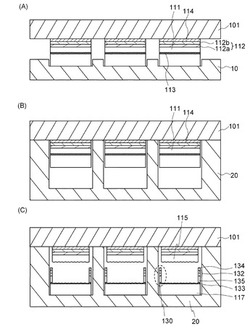

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、パターニング後、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力をパターン側面を含めて開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

電気光学装置および電子機器

【課題】素子基板の基板本体として半導体基板を用いた場合でも、複雑なウエル構造や大掛かりな遮光構造を必要とせず、かつ、基板本体としてガラス基板などを用いた場合に比較して画素トランジスターの特性を大幅に向上することのできる電気光学装置、および当該電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置100の素子基板10では、基板本体として、単結晶シリコン基板からなる半導体基板11を用い、半導体基板11の表面に不純物を導入することによって、バックゲート構造を備えた画素トランジスター30の第1ゲート電極11a、および保持容量60の第1保持容量電極11bを同時形成する。また、第1ゲート絶縁層70の一部を保持容量用誘電体層70cとして利用する。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

コンタクト形成方法、半導体装置の製造方法、および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】半導体と接した第1の金属層を酸化防止用の第2の金属層で覆った状態で、第1の金属層のみをシリサイド化し、酸素混入のないシリサイド層を形成する。第1の金属層の材料として、半導体との仕事関数の差が所定の値となるような金属が用いられ、第2の金属層の材料として、アニール温度で第1の金属層と反応しない金属が用いられる。

(もっと読む)

薄膜トランジスタ及び電気光学装置、並びに電子機器

【課題】例えば、画素スイッチング用素子として用いられる薄膜トランジスタについて、そのサイズを小さくすることによって生じる可能性があるON電流の減少を抑制する。

【解決手段】下地部(13)は、TFTアレイ基板(10)の基板面を基準としてTFTアレイ基板(10)の図中上側に向かって突出した凸部であり、下地絶縁膜(12)の一部として一体として、又は下地絶縁膜(12)とは別に形成されている。下地部(13)の表面(13s)は、面(13s−1)と、面(13s−2)とから構成されている。チャネル領域(1c)は、該チャネル領域(1c)が表面(13s)に沿って延びるように形成されている。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに、電気光学装置及び電子機器

【課題】例えば、液晶装置において、画素ピッチの微細化に対する要請に応じつつ、当該微細化によって得られるべき表示性能の向上を十分に享受可能な薄膜トランジスタを提供する。

【解決手段】ドレイン領域(1d)の夫々の幅(W1)は、幅方向に沿って、チャネル領域(1c)の幅(W3)より細い。加えて、ドレイン領域(1d)の夫々の厚み(T1)は、チャネル領域(1c)の厚み(T3)より薄い。したがって、TFT(30)のドレイン領域(1d)の側面及び上面からなる表面の面積は、比較例に係るTFTのドレイン領域の表面の面積より小さい。よって、TFT(30)によれば、ゲート電極(3a2)で遮光されないドレイン領域(1d)の夫々の表面積を低減することができ、TFT(30)の上側から3次元的に照射される光のうちドレイン領域(1d)が受ける光量を低減することが可能であり、光リーク電流を低減することができる。

(もっと読む)

半導体装置

【課題】半導体膜からなるダイオードを適用した保護回路の性能を向上させる。

【解決手段】2つの入出力端子の間に保護回路が挿入されている。保護回路は、絶縁表面上に形成される半導体膜からなるダイオードを含む。ダイオードのN型不純物領域およびP型不純物領域を保護回路の1層目の導電膜と接続するためのコンタクトホールは、各不純物領域全体に分布して形成される。また、保護回路の1層目の導電膜と2層目の導電膜とを接続するためのコンタクトホールは、半導体膜上に存在し、かつ分散して形成される。このようにコンタクトホールを形成することで、ダイオードと端子間の配線抵抗を低減し、かつダイオードの半導体膜全体を整流素子として有効に機能させることができる。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】良好な結晶性を有し、S値において高性能な半導体素子を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定し、単結晶半導体層にレーザ光を照射し、単結晶半導体層を部分溶融状態として再単結晶化し、結晶欠陥を修復する。次いで、n型トランジスタとなる島状単結晶半導体層にフォトマスクを用いてチャネルドープし、次いで該フォトマスクを用いて島状単結晶半導体層をエッチバックし、p型トランジスタとなる島状単結晶半導体層の膜厚より薄くなるようにする。

(もっと読む)

反射型電気光学装置および投射型表示装置

【課題】迷光を発生させることなく、隣接するデータ線間の干渉を防止することのできる反射型電気光学装置および投射型表示装置を提供すること。

【解決手段】反射型電気光学装置100において、素子基板10では、X方向で隣接するデータ線6aに挟まれた領域にY方向に延在する透光性導電膜からなるシールド線7aが形成されているため、X方向で隣接するデータ線6a同士の間に寄生する容量が極めて小さい。素子基板10において、基板10dは透光性基板であり、シールド線7aは透光性導電膜からなるため、対向基板20側から入射した光が画素電極9aで挟まれた隙間領域9sで漏れて素子基板10側に入射した際、かかる光はシールド線7aを透過した後、基板10dを透過する。従って、シールド線7aでの反射に起因する迷光の発生を防止することができる。

(もっと読む)

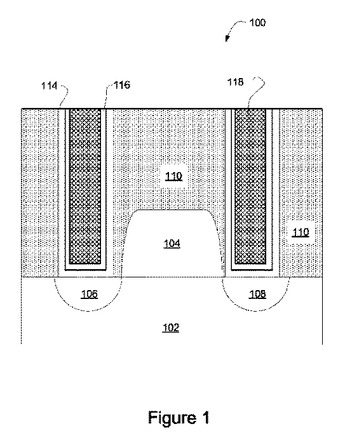

金属ヒューズ、アンチヒューズ及び/又は抵抗器を含む金属ゲート統合構造体及び方法

【課題】 個々の半導体デバイス・コンポーネントの統合の強化、製造性の向上をもたらす、半導体構造体及びそれらの半導体構造体を製造する方法を提供する。

【解決手段】 半導体構造体及び半導体構造体を製造するための方法が、半導体基板の活性領域上に配置及び形成された電界効果デバイスと、半導体基板内の活性領域から横方向に分離された分離領域上に少なくとも部分的に同時に配置及び形成された、ヒューズ構造体、アンチヒューズ構造体及び抵抗器構造体の少なくとも1つとを提供する。電界効果デバイスは、高誘電率の誘電体材料を含むゲート誘電体と、金属材料を含むゲート電極とを含む。ヒューズ構造体、アンチヒューズ構造体及び抵抗器構造体の少なくとも1つは、ゲート誘電体と同じ材料を含むパッド誘電体と、随意的に、同様にゲート電極と同じ金属材料を含むことができるヒューズ、アンチヒューズ又は抵抗器とを含む。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 優れたコンタクト特性及び優れた素子特性を持った薄膜半導体装置及びその製造方法を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて不純物を含むソース領域ドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成されたコンタクト孔内にそれぞれ埋め込まれた不純物を含む多結晶半導体層、及び前記多結晶半導体層に接続する高融点金属層を含む配線層を具備し、前記多結晶半導体層と配線層の高融点金属層との間には、高融点金属と半導体との化合物からなる薄層が形成されていることを特徴とする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

単結晶半導体膜の結晶性評価方法及び半導体基板の作製方法

【課題】良好な結晶性を有し高性能な半導体素子を形成することを可能とする半導体基板を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定し、単結晶半導体層にレーザ光を照射し、単結晶半導体層を部分溶融状態として再結晶化し、結晶欠陥を修復する。再結晶化後の単結晶半導体層は深さ方向の濃度分布において、炭素濃度が極大を有する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】膜厚バラツキを抑制し、かつドライエッチングダメージの発生を抑制できる優れた素子特性を兼ね備えた薄膜半導体装置及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極、前記ゲート電極の側壁に形成された、低温酸化膜、低温窒化膜及び低温酸化膜の3層構造のサイドウォールスペーサー、及び島状半導体層及びゲート電極を覆う層間絶縁膜を具備することを特徴とする。

(もっと読む)

41 - 60 / 187

[ Back to top ]