Fターム[5F110HL05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | シリサイド (187)

Fターム[5F110HL05]に分類される特許

141 - 160 / 187

薄膜トランジスタ、その製造方法、半導体装置及び表示装置

【課題】寄生トランジスタの発生を抑制することができ、高性能化を図ることができ、かつゲート絶縁耐圧劣化を抑制することで高信頼性を得ることができる薄膜トランジスタ、その製造方法、半導体装置及び表示装置を提供する。

【解決手段】ゲート絶縁膜を挟んで半導体層とゲート電極とが交差配置された構造を有する薄膜トランジスタであって、上記半導体層は、チャネル部の端部が傾斜しており、上記ゲート絶縁膜は、チャネル部の端部と重なる部分の酸化シリコン換算膜厚が、チャネル部の中央部と重なる部分の酸化シリコン換算膜厚よりも大きい薄膜トランジスタ。

(もっと読む)

電気光学装置用基板、電気光学装置、電子機器及び電気光学装置用基板の製造方法

【課題】新たなフォトマスクを必要とすることなく配線とソース・ドレイン領域との接触抵抗を低減させることが可能な電気光学装置用基板、電気光学装置、電子機器及び電気光学装置用基板の製造方法を提供すること。

【解決手段】液晶表示装置100aは、TFT基板10a及び対向基板20aを有する。TFT基板10aには、TFT素子30、データ線6aが形成されている。TFT素子30の高濃度ソース領域1dのうちデータ線6aと接する部位には、チタンシリサイドの層が形成されている。同様に、容量電極300のうちシールド層用中継層6a1と接する部位、及び中継電極719のうち第2中継電極6a2と接する部位にも、チタンシリサイドの層が形成されている。これにより、接触抵抗を低減することができる。

(もっと読む)

3次元半導体デバイスの製造方法

【課題】 半導体素子の回路が形成されているSi層上に絶縁膜を形成し、該絶縁膜上に多結晶もしくは非晶質Si層を積層し、これをレーザー照射及び走査により(再)結晶化して、ここに別の半導体素子の回路を形成し、これらの回路を接続する3次元半導体デバイスの製造方法に関する。レーザー(再)結晶化Si層の結晶性を改良することにより、現在のICに適した性能を与える。

【解決手段】絶縁膜17,26をCMPにより平坦化する;多結晶又は非晶質Si層22,32を積層し、エネルギーが照射面積当たり10J/cm2以上の固体連続波レーザーにより照射・走査行う;その直後にレーザーアニールを行う。

(もっと読む)

印刷式自己整合トップゲート型薄膜トランジスタ

【課題】高性能のトップゲート型TFTを印刷方式で製造することを可能にする薄膜トランジスタを提供する。

【解決手段】半導体薄膜層2を形成するステップと、その上に、TFTのチャネル領域を画成するギャップ5が形成されたドープトガラスパターン4を印刷するステップと、チャネル領域の上又は上方に、ゲート誘電体膜及びこの上のゲート伝導体3を有するゲート電極を形成するステップと、ドープトガラスパターンから半導体薄膜層にドーパントを拡散させるステップとを含む自己整合トップゲート型薄膜トランジスタ(TFT)及びそのような薄膜トランジスタの製造方法。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置の製造方法並びに薄膜トランジスタ

【課題】本発明の目的は、半導体膜を大粒径の結晶化が可能な半導体装置の製造方法を提供することである。

【解決手段】半導体装置の製造方法は、非単結晶半導体膜の結晶化領域に、光変調されて極小光強度線もしくは極小光強度点を有する光強度分布のレーザ光を前記非単結晶半導体膜上に設けられた第1の光吸収層を介して照射して前記結晶化領域を結晶化するレーザ照射工程、即ち結晶化工程(A)と、少なくとも結晶化された前記結晶化領域の上に形成された第2の光吸収層にレーザ光もしくはフラッシュランプ光を照射することにより前記結晶化された領域を第2の光吸収層を介して再加熱する再結晶化工程、即ち加熱工程(C)とを有する。

(もっと読む)

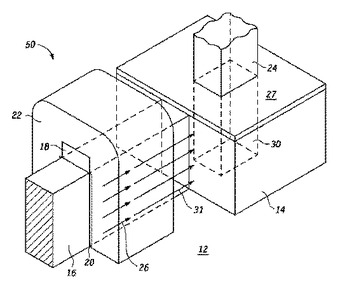

埋没接点を有するトランジスタとその形成方法

第1の電流電極領域(32)、第2の電流電極領域(34)、およびチャネル領域(37)を含む半導体構造の形成方法であって、チャネル領域(37)は第1の電流電極領域(32)と第2の電流電極領域(34)との間に配置され、チャネル領域(37)は半導体構造のフィン構造(36)内に配置され、チャネル領域内のキャリア輸送は概して第1の電流電極領域(32)と第2の電流電極領域(34)との間で水平方向に行われる方法。該方法は、第1の接点(66)を形成することを含み、第1の接点(66)を形成することは、半導体構造の第1の部分を除去して、第1の電流電極領域(32)に開口部(54)を形成すること、開口部に接点材料(66)を形成することを含む。  (もっと読む)

(もっと読む)

結晶化方法、薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、半導体装置

【課題】 高い移動度と移動度や閾値電圧特性のバラツキの小さいTFTを得ることができる結晶化方法、薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、半導体装置を提供する。

【解決手段】 絶縁性基板上に設けた40乃至100nmの非単結晶半導体薄膜にレーザ光を照射して結晶化する際に、基板表面上で逆ピークパターンを有する光強度分布を形成して、この光強度分布の光強度勾配を制御して、幅より結晶成長方向に長い形状で粒長方向に{100}に優先配向した結晶化粒4を配列させた結晶化粒列を形成し、この結晶化粒列の複数の結晶化粒に跨がり結晶成長方向に電流が流れるようにソース領域およびドレイン領域を設けてTFTを形成する。

(もっと読む)

酸化物半導体薄膜トランジスタを用いた発光素子及びこれを用いた画像表示装置

【課題】電子キャリア濃度が1018/cm3未満の酸化物を用いたTFTを有し、安定的に動作する発光素子を提供する。

【解決手段】発光素子は、基板101上に青、緑、及び赤の光の3原色に対応する青色画素領域a1、緑色画素領域a3、及び赤色画素領域a2を有する画素領域を備える。この画素領域に、ソース電極105、ドレイン電極100、ゲート電極104、ゲート絶縁膜103、及び活性層102を有するTFT11と、発光層108と、この発光層108を挟む下部電極107及び対向電極109とを有する。活性層108は、酸化物で構成される。ドレイン電極100は、下部電極107を介して発光層108の一部に電気的に接続される。TFT11は、基板101上の青色画素領域a1を除く領域、例えば赤色画素領域a2に配置される。

(もっと読む)

表示装置およびその製造方法

【課題】表示装置の遮光性及び配向性を同時に改善する。

【解決手段】表示装置は、基板11上に透明画素電極31を駆動する薄膜トランジスタが設けられ、この薄膜トランジスタの上層でかつ画素電極31の下層の位置に導電性の遮光層27,28が設けられている。第一の平坦化膜25が薄膜トランジスタの凹凸を埋める様に形成されており、その平坦化された表面に遮光層27,28が配されている。第二の平坦化膜29が遮光層27,28の段差を埋める様に形成されており、その平坦化された表面に画素電極31が配されている。導電性の遮光層27,28を上下から絶縁性の平坦化膜29,25で挟み込む構造を採用することで、表示装置の遮光性及び配向性を改善することが可能である。

(もっと読む)

駆動電流を減少させずにしきい値をさらに安定させるトランジスタデバイス

ハロ領域(206、306)の一部を除去することにより、あるいは、再成長した半導体材料(218、318)に基づいて続いて形成される延長領域(209A)内にハロ領域(206)を形成しないようにすることで、しきい値のロールオフ挙動が非常に改善される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート幅方向の各位置における閾値電圧をばらつかせることなく、基板浮遊効果を抑制することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】支持基板11aとBOX層11bとSOI層11cとを有するSOI基板11と、SOI層11c上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14と、SOI層11cにおけるゲート電極14端下の領域に形成された第1導電型の低濃度領域15bと、ゲート電極14下であってSOI層11cにおける低濃度領域15bで挟まれた領域に形成され、低濃度領域15bよりも不純物濃度が高い第1導電型の高濃度領域15aと、SOI層11cにおける高濃度領域15a及び低濃度領域15bを挟む一対の領域に形成され、第2導電型のソース領域16s及びドレイン領域16dとを有する。

(もっと読む)

TFTアレイ基板、液晶パネル及び電子機器

【課題】TFT駆動によるアクティブマトリクス駆動方式の液晶パネルにおいて、TFTの下側に遮光層を設ける構成を利用して、効率良く画素部を平坦化する。

【解決手段】液晶パネル(100)は、一対の基板間に挟持された液晶層(50)と、TFTアレイ基板(10)にマトリクス状に設けられた画素電極(11)とを備える。遮光層(3)は、TFT(30)及び容量線(3b)を下側からみて重なるように配置する。遮光層(11a)が形成されている領域においては遮光層上に、且つ遮光層が形成されていない領域においてはTFTアレイ基板上に設けられた第1層間絶縁層(12、13)は、TFT、容量線等に対向する部分が対向基板の側から見て凹状に窪んで形成されている。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

ドープされた半導体物質のエピタキシャル堆積

炭素ドープされたエピタキシャル半導体薄膜(30)の堆積方法であって、露出した単結晶物質(20)を有するパターニングされた基板(10)を収容するプロセスチャンバ(122)内を、約700torrより高い圧力に維持するステップを含む。前記方法はさらに、プロセスチャンバ(122)に、シリコンソースガスのフローを供給するステップを含む。前記シリコンソースガスはジクロロシランを含む。前記方法はさらに、プロセスチャンバ(122)に、炭素前駆物質(132)のフローを供給するステップを含む。前記方法はさらに、露出した単結晶物質(20)上に、炭素ドープされたエピタキシャル半導体薄膜(30)を選択的に堆積するステップを含む。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】Fin型トランジスタの金属ゲート電極を高抵抗化させることなく、トランジスタを正常に動作させることができる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、半導体材料から成り、上面が保護膜40で被覆されたFin30を絶縁層20上に形成し、Finの側面にゲート絶縁膜50を形成し、Finを被覆するようにゲート電極材料60を堆積し、ゲート電極材料を平坦化し、ゲート電極材料を加工することによってゲート電極62を形成し、ゲート電極を被覆するように層間絶縁膜90を堆積し、ゲート電極の上面を露出させ、ゲート電極の上面上に金属110を堆積し、ゲート電極と金属とを反応させることによってゲート電極をシリサイド化し、金属のうち未反応の金属を除去することによって、保護膜の上面上に溝115が形成され、溝に導電体120を充填することを具備する。

(もっと読む)

CMOS対応の浅いトレンチのeフューズ構造体及びその製造方法

【課題】 少なくとも1つのeヒューズを含む半導体構造体と標準的な半導体技術との統合が容易であり、よって実施コストが最小になる製造方法を提供する。

【解決手段】 半導体基板(バルク又は半導体オン・インシュレータ)内に配置されたトレンチ内に埋め込まれた少なくとも1つのeヒューズを含む半導体構造体が提供される。本発明によると、eヒューズは、半導体基板内に配置されたドーパント領域と電気接触した状態にある。本発明はまた、埋め込まれたeヒューズが、トレンチ分離領域とほぼ同時に形成される半導体構造体を製造する方法も提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子間の電気的な分離を向上しつつ、素子形成領域の縮小及び駆動能力の向上が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11から電気的に分離されると共に、ゲート幅方向に配列する複数の島状領域10aに分断された素子形成領域10Aと、複数の島状領域10aに跨るように形成されたゲート電極15a及び15bと、島状領域10a上部に形成されたp型ボディ領域17と、p型ボディ領域17上部に形成されたソース領域18s及びボディ引上げ領域19と、島状領域10a上部に形成されたドレイン領域18dと、複数のドレイン領域18d又は複数のソース領域18s及びボディ引上げ領域19と電気的に接続されたコンタクト内配線22及びメタル配線23とを有する。

(もっと読む)

エキシマレーザーアニール法で作製したSi膜を用いた半導体トランジスタ製造方法

【課題】位相変調されたエキシマレーザーによる結晶化法において、半導体膜の結晶化を容易にする。

【解決手段】絶縁基板(31)上に形成された半導体薄膜(32)を結晶化する方法であって、入射されたコヒーレント光の位相分布を変更する位相シフタ部(33、34、35’)を前記半導体薄膜上に形成する工程と、前記半導体薄膜にコヒーレント光を照射し、前記半導体薄膜(32)に前記位相シフタ部に対応する温度分布を形成して、前記半導体薄膜の少なくとも一部を溶融する工程と前記コヒーレント光の照射を中止して前記溶融部の温度を低下させ、溶融された半導体を結晶化する工程とを有する方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】基板上にトランジスタ等の半導体素子とセンサーとを作り込んで設ける場合に、同一工程で作製することにより得られる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】同一基板上に、互いに接する第1の領域および第2の領域を有する第1の半導体膜と、チャネル領域とソースまたはドレイン領域として機能する第3の領域とを有する第2の半導体膜と、第1の半導体膜および第2の半導体膜を覆って設けられた絶縁膜と、絶縁膜上に設けられ且つ第1の領域と電気的に接続する第1の導電膜と、第2の領域と電気的に接続する第2の導電膜とを設け、第1の領域、第2の領域および第3の領域に不純物元素を第1の領域と第2の領域に含まれる不純物元素の濃度が異なるように導入する。

(もっと読む)

141 - 160 / 187

[ Back to top ]