Fターム[5F110HL05]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | シリサイド (187)

Fターム[5F110HL05]に分類される特許

21 - 40 / 187

対向電極を有する小型電界効果トランジスタおよび製造方法

【課題】小型化の増進を可能にするとともに、実現が容易な、対向電極を備えた電界効果トランジスタの製造方法を提供する。

【解決手段】ゲート電極9ソースコンタクト12,ドレインコンタクト13、および対向電極コンタクトの輪郭描写パターンを含むエッチングマスクが、セミコンダクタ・オン・インシュレータ型の基板上に形成される。基板は、誘電体5の層およびゲート材料により覆われる。対向電極コンタクトは、ゲート電極9のパターン内に配置される。ゲート材料は、ゲート電極9、ソースコンタクト12およびドレインコンタクト13、ならびに対向電極コンタクトを画定するためにエッチングされる。支持基板2の一部分は、対向電極コンタクト領域のパターンの中を通って解放される。導電性材料22が支持基板2の自由部分上に堆積されて、対向電極コンタクトを形成する。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

半導体装置

【課題】不揮発性記憶装置と揮発性記憶装置の双方のメリットを享受する記憶装置を提供する。

【解決手段】基板または基板上に設けられた第1のトランジスタと、第1のトランジスタよりも上に設けられた第2のトランジスタを有する半導体装置において、第1のトランジスタと第2のトランジスタの少なくとも一部を重畳させ、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極を電気的に接続させる。第1のトランジスタとしてはシリコン単結晶により設けられたものが好ましく、第2のトランジスタとしてはオフ電流が極端に小さい酸化物半導体により設けられたものが好ましい。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

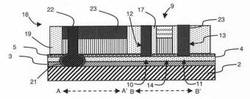

埋め込み絶縁層を貫いて半導体層間に接触を有するデバイス、およびこのデバイスの製造プロセス

【課題】簡潔な方法で、SeOI基板上の半導体デバイスの半導体領域に接続するラインを提供すること。

【解決手段】第1の側面によると、本発明は埋め込み絶縁層(3、BOX)によってベース基板(2)から隔離された半導体材料の薄い層(1)を含むSeOI(Semiconductor−On−Insulator)基板上に作製された半導体デバイスに関し、デバイスは、薄い層内に第1の伝導領域(1、D1、S、E)と、ベース基板内に第2の伝導領域(5、BL、SL、IL)とを含み、接触(I1、I2、IN、IP)は絶縁層を貫通して第1の領域と第2の領域を接続する。第2の側面によると、本発明は第1の側面に関する半導体デバイスの製作プロセスに関する。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)と半導体基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。

【解決手段】溝部が設けられた半導体基板に、イオンを照射して半導体基板中に脆化領域を形成し、絶縁層を介して半導体基板とベース基板を貼り合わせると共に、半導体基板の溝部とベース基板とにより囲まれた空間を形成し、熱処理を施すことにより、脆化領域において半導体基板を分離して、ベース基板上に絶縁層を介して半導体層を形成する。

(もっと読む)

窒化物半導体素子

【課題】ゲート絶縁膜の絶縁破壊を抑制または防止できる構造を有する窒化物半導体素子を提供する。

【解決手段】電界効果トランジスタ1(窒化物半導体素子)は、窒化物半導体の積層構造部3と、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、ガードリング層11とを含む。積層構造部3は、n型GaN層4,5、p型GaN層6およびn型GaN層7を積層して構成されている。ゲート絶縁膜15は、n型GaN層5、p型GaN層6およびn型GaN層7に跨るように、積層構造部3の壁面9に形成されている。ゲート電極16は、ゲート絶縁膜15を挟んでp型GaN層6に対向している。ガードリング層11は、p型GaN層6における壁面9に間隔を開けて対向するようにn型GaN層5上に形成されたp型GaN層からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】高解像度のイメージングセンサにおいても、十分な光電流を得ることができる半導体装置を提供する。

【解決手段】薄膜ダイオード200Aは、第1および第2半導体領域233、234を有する第1半導体層230と、第1半導体層230上に形成された第2および第3半導体層236、238と、第1および第2コンタクトホール241、242とを有する。第1半導体領域233は、第1導電型不純物を含有し、第2半導体領域236および第3半導体層238は、第2導電型不純物を含有し、第2半導体層236は、第2導電型不純物とは異なる第3導電型不純物を含有し、第2および第3半導体層236、238は、選択成長により形成され、第2半導体領域234は第2コンタクトホール242に整合している。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、チャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、不純物領域と電気的に接続する第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の第2のゲート電極と、第2のゲート電極上の第2のゲート絶縁層と、第2のゲート絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続する第2のソース電極および第2のドレイン電極と、を有する第2のトランジスタと、を有する半導体装置である。

(もっと読む)

半導体装置

【課題】従来のメモリ素子とは異なり、軟化又は溶融といった状態変化を利用したメモリ素子を提供し、メモリ容量が増大されたメモリ装置を提供することを課題とする。

【解決手段】一対の電極間に、ガラス転移温度が異なる複数のメモリ材料層を積層させたメモリ素子である。ガラス転移温度は10℃以上の差があると好ましい。このようなメモリ素子に電圧を印加することで、複数のメモリ材料層を一つずつ軟化又は溶融させる。このような構成により、メモリ容量が3値以上となり増大される。

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)とボンド基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。または、上記荒れを抑えて半導体装置の歩留まりを向上することを目的の一とする。

【解決手段】ボンド基板にイオンを添加して該ボンド基板に脆化領域を形成し、ベース基板にレーザー光の照射による複数の凹凸部を形成し、絶縁層を介してボンド基板とベース基板とを貼り合わせる際に、複数の凹凸部をボンド基板とベース基板との位置合わせの指標として用いると共に、複数の凹凸部の一を含む領域に、ボンド基板とベース基板とが貼り合わない領域であってその外周が閉じられた領域を形成し、熱処理を施すことにより、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成する。

(もっと読む)

半導体装置の作製方法

【課題】半導体膜への不純物の拡散を抑えつつ、歩留まりの低下を抑えることができるSOI基板の作製方法を提供することを、目的の一とする。

【解決手段】半導体基板の表面を熱酸化させることで、酸化膜が形成された半導体基板を形成する。そして、窒素原子を有するガス雰囲気下においてプラズマを発生させることにより、上記酸化膜の一部をプラズマ窒化させ、酸化膜上に窒素原子を含む絶縁膜が形成された半導体基板を得る。そして、窒素原子を含む絶縁膜とガラス基板を接合させた後、半導体基板を分離することで、ガラス基板上に窒素原子を含む絶縁膜、酸化膜、薄膜の半導体膜が順に積層されたSOI基板を形成する。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】平坦性を確保しつつ、結晶性の高い半導体膜を有する、SOI基板の作製方法を提供することを、目的の一とする。

【解決手段】分離により絶縁膜上に単結晶の半導体膜を形成した後、該半導体膜の表面に存在する自然酸化膜を除去し、半導体膜に対して第1のレーザ光の照射を行う。第1のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を7以上、より好ましくは10以上100以下とする。そして、第1のレーザ光の照射を行った後、半導体膜に対して第2のレーザ光の照射を行う。第2のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を0より大きく2以下とする。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

レーザ照射装置及び半導体基板の作製方法

【課題】半導体膜の結晶性若しくは表面の平坦性、又は結晶性及び表面の平坦性を高めることのできるレーザ照射装置を提供することを目的の一とする。

【解決手段】レーザ発振器と、レーザ発振器から射出されたレーザ光を線状に成形する光学系と、光学系によって成形された線状のレーザ光が照射される被照射物を載置するステージと、を有し、ステージは、支持台上に、ヒータ、不純物吸着材及び被照射物を載置する載置台が順に固定されているレーザ照射装置を用いて、絶縁表面上に設けられた半導体膜にレーザ光を照射し、半導体膜を結晶化する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体デバイス及びその形成方法

【課題】応力ライナによるコンタクト形成の問題が起きない、相補型金属酸化膜半導体(CMOS)デバイスの製造方法を提供する。

【解決手段】シリコン基板層上の二酸化シリコン層102と、凹んだソース/ドレイン・トレンチを有する相補型金属酸化膜半導体(CMOS)デバイスを準備し、凹んだソース/ドレイン・トレンチ内に窒化物応力ライナ104を堆積し、その上に酸化物層106を堆積する。CMOSデバイスをハンドリング・ウェハ上に置きシリコン基板層を除去し二酸化シリコン層102をエッチングしてソース/ドレイン領域170の一部に当接する開口部を形成しコンタクト180を形成する。

(もっと読む)

21 - 40 / 187

[ Back to top ]