Fターム[5F110NN03]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935) | 複数層 (3,316)

Fターム[5F110NN03]に分類される特許

3,201 - 3,220 / 3,316

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜42を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜42を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極に接続される導電体層35、36とを接続するための上層接続配線49、52、55、58は、トップゲート電極8を覆う層間絶縁膜40上に設けられている。

(もっと読む)

半導体装置およびその作製方法

【課題】 従来のパルス発振のレーザー光による照射を半導体膜に行った場合、半導体表面にリッジと呼ばれる凹凸が形成され、トップゲート型TFTの場合には、素子特性がリッジにより大きく左右されていた。特に、電気的に並列に接続する複数の薄膜トランジスタ間でのバラツキが問題となっている。

【解決手段】 本発明は、複数の薄膜トランジスタからなる回路の作製において、連続発振レーザを用いて半導体膜にレーザ光を照射して溶融する領域の幅LP(微結晶領域を含まない)を大きくし、一つの領域に複数の薄膜トランジスタ(電気的に並列に連結された薄膜トランジスタ)の活性層を配置することを特徴の一つとする。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 光電気変換型の薄膜トランジスタ3のアモルファスシリコンからなる半導体薄膜41は、駆動回路用のCMOS薄膜トランジスタ21、22のポリシリコンからなる半導体薄膜25、26よりも上層側に設けられている。これにより、半導体薄膜41を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のソース・ドレイン電極10は、薄膜トランジスタ21、22のソース・ドレイン電極を含む導電体層34、35と同一の層(オーミックコンチクト層43を含むボトムゲート絶縁膜31)上に同一の導電材料(モリブデン)によって同時に形成されている。

(もっと読む)

レーザ照射装置およびレーザ照射方法

【課題】半導体膜全面に対して均一にレーザ処理を行うことができるレーザ照射装置を提供すること、およびレーザ照射方法を提供すること。

【解決手段】第1のレーザ発振器より出射された第1のレーザビームは、スリットを通し、さらに集光レンズを通した後に照射面に入射させる。同時に、照射面において第2のレーザ発振器より出射された第2のレーザビームを第1のレーザビームに重ねて照射する。さらに、照射面に対して相対的に走査することによって、照射面を等しくアニールする。

(もっと読む)

回路基板、電気光学装置、及び電子機器

【課題】 トランジスタ等の能動素子が安定に動作し、大画面化と長期にわたって安定した表示動作とを可能にする。

【解決手段】 陰極(222)と陽極(23)とに狭持され、基板(2)の上方に配置された電気光学素子と、電気光学素子を駆動する能動素子(24)と、陰極(222)及び陽極(23)のうち少なくとも一方と基板(2)との間に配置された誘電率が所定の値以下の絶縁材料からなる絶縁膜(283、284)とから電気光学装置(1)を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ボディコンタクトを有するSOIデバイスにおいて、ボディコンタクトとボディ領域との間に所望の抵抗値を持たせると共に、当該抵抗値のばらつきを抑制する。

【解決手段】SOI層3におけるコンタクト61との接続部分(即ち、素子分離絶縁膜41の下)に、不純物濃度の高いP+領域を形成せずに、SOI層3とボディコンタクト61とをショットキー接合させる。また、ボディコンタクト61の表面にはバリアメタル61aが形成されており、ボディコンタクト61とSOI層3との間に、バリアメタル61aとSOI層3とが反応したシリサイド70が形成される。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた画像読取装置において、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極に接続される導電体層35、36とを接続するための上層接続配線48、51、54は、ボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8の各電極と同一の層に、同一の導電材料により形成され、下層接続配線50、53、56は、導電体層35、36と同一の層に、同一の導電材料により形成される。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜41を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極を含む導電体層35、36とを接続する接続配線の一部である上層接続配線48、51、54は、トップゲート電極8が設けられたトップゲート絶縁膜39上に設けられている。

(もっと読む)

薄膜集積回路の剥離方法および半導体装置の作製方法

【課題】 低コストで生産効率がよい薄膜集積回路の剥離方法および当該剥離方法を用いたICチップの作製方法の提供を課題とする。

【解決手段】 基板上に金属を含んだ膜からなる剥離層を形成し、その剥離層上に複数の薄膜集積回路を形成し、複数の薄膜集積回路上にそれぞれ樹脂膜を形成し、剥離層にフッ化ハロゲンを含む気体または液体を導入して、剥離層を除去して、基板と薄膜集積回路とのを剥離を行う。また、剥離した薄膜集積回路を、ラミネート等により封止することによってICチップを形成する。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、画素電極及びデータ線間に生じる容量カップリングの影響を極力排除するとともに、TFTの長期寿命化を図り、更には、積層構造を構成する各要素間の電気的接続を良好に実現することによって、より高品質な画像を表示する。

【解決手段】基板上に、データ線(6a)、走査線(3a)、画素電極(9a)及びTFT(30)が積層構造の一部をなして備えられている。この基板上には更に、TFT及び画素電極に電気的に接続された蓄積容量(70)と、データ線及び画素電極間に配置されたシールド層(400)と、前記画素電極の下地として配置された層間絶縁膜(43)とが、前記積層構造の一部をなして備えられている。このうちシールド層は略三角形の部分が設けられ、前記略三角形の部分も含めて窒化膜を含む。

(もっと読む)

剥離および封止可能な装置、ICシート、ICシートの巻物およびICチップの作製方法

【課題】 薄膜集積回路の封止の際の製造効率の悪化を防止し、損傷や破壊を防止することを課題とする。また、基板からの薄膜集積回路の剥離および剥離した薄膜集積回路の封止を効果的に行い、製品の歩留まりを向上させることを課題とする。

【解決手段】 薄膜集積回路が複数設けられた基板を搬送する搬送手段と、薄膜集積回路の一方の面を第1のシート材に接着させて、基板から薄膜集積回路を剥離する第1の剥離手段と、薄膜集積回路の他方の面を第2のシート材に接着させて、第1のシート材から薄膜集積回路を剥離する第2の剥離手段と、薄膜集積回路を第2のシート材と第3のシート材で挟み込み、薄膜集積回路を封止するラミネート手段とを有するラミネート装置を提供する。

(もっと読む)

アクティブマトリクス基板及びそれを用いた容量性表示装置

【課題】

開口率が高いアクティブマトリクス基板を提供する。

【解決手段】

本発明に係るアクティブマトリクス基板1は、容量形成用のトレンチ64を有する容量形成部a表面に形成された基板60と、基板60の容量形成部a以外の部分の上に設けられ、ゲート絶縁層41を有するTFT40と、基板60の容量形成部aの上に設けられ、誘電層51を有する補助容量素子50と、を有し、誘電層51とゲート絶縁層41とは、同一膜で形成されており、誘電層51の層厚はゲート絶縁層51の層厚よりも薄いものである。

(もっと読む)

歪みFinFETCMOSデバイス構造

【課題】移動度を高めたダブル・ゲートCMOSデバイス構造を提供すること。

【解決手段】本発明によれば、半導体デバイス構造は、基板(1、2)上に配置されたPMOSデバイス(200)およびNMOSデバイス(300)を含み、このPMOSデバイスはこのPMOSデバイスの活性領域に応力を加える圧縮層(6)を含み、このNMOSデバイスはこのNMOSデバイスの活性領域に応力を加える引張り層(9)を含み、この圧縮層は第1の誘電体材料を含み、この引張り層は第2の誘電体材料を含み、これらのPMOSおよびNMOSデバイスはFinFETデバイス(200、300)である。  (もっと読む)

(もっと読む)

アクティブマトリクス型表示装置およびアクティブマトリクス型表示装置の製造方法

【課題】 容易な構造で、有機絶縁膜からの水分の放出を防止できるアクティブマトリクス型表示装置を提供する。

【解決手段】 アクティブマトリクス型表示装置は、TFT2との電気的な接続を行なうためのコンタクトホール4aを含む有機絶縁膜4と、有機絶縁膜4の表面の少なくとも一部に形成された画素メタル電極7aとを備える。有機絶縁膜4は、隣り合う画素の画素メタル電極7aを互いに分離するように形成された第1溝部4bを含む。

(もっと読む)

表示装置及びその作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する表示装置の作製方法を提供する。

【解決手段】 本発明の表示装置の一は、絶縁表面上に設けられたソース電極層、ドレイン電極層及び画素電極層を有し、ソース電極層及びドレイン電極層上に一導電型を有する半導体層を有し、一導電型を有する半導体層上に結晶性半導体層を有し、結晶性半導体層に接してゲート絶縁層を有し、ゲート絶縁層に接してゲート電極層を有し、ゲート絶縁層、ゲート電極層、及び画素電極層上に絶縁層を有し、ゲート絶縁層及び絶縁層は、ソース電極層またはドレイン電極層に達する第1の開口部、及び画素電極層に達する第2の開口部を有し、第1の開口部及び第2の開口部に、ソース電極層またはドレイン電極層と画素電極層とが電気的に接続する配線層を有する。

(もっと読む)

半導体装置および半導体装置の作製方法

(課題)

本発明は、被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、本発明は、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子(薄膜ダイオード、シリコンのPIN接合からなる光電変換素子やシリコン抵抗素子)を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)

基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化を行い金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。  (もっと読む)

(もっと読む)

表示装置用駆動回路

【課題】 長時間の駆動に対しても信頼性の高い表示装置用駆動回路を提供する。

【解決手段】 互いに接続され、順次に出力信号をそれぞれ生成する複数のステージを有する表示装置用駆動回路であって、前記各ステージは、複数のトランジスタを有し、前記各トランジスタは、制御電極と、前記制御電極上に形成される第1絶縁膜と、前記第1絶縁膜上に形成される半導体層と、前記半導体層上に少なくとも一部分が形成される入力電極と、前記半導体層上に少なくとも一部分が形成される出力電極と、前記入力電極及び出力電極上に形成される第2絶縁膜とを備え、前記半導体層と前記第1絶縁膜の厚さとの比が、0.3〜1.5である。

(もっと読む)

液晶用マトリクス基板およびその製造方法

【課題】 表示品位が高く、周辺回路とのコンタクト性に優れた液晶表示装置を構成するマトリックス基板およびその製造方法を実現する。

【解決手段】 複数の液晶セルを形成するためのマトリクス回路が形成されている液晶用マトリクス基板において、液晶パネルを組み立てるときに貼り合わせ面となる表面に島状に、第1の導電材からなる絵素電極12と、第2の導電材からなる端子電極13とを形成する。このとき、第1の導電材は、第2の導電材よりも透過性が高く、かつ、導電性が低いものを使用する。

(もっと読む)

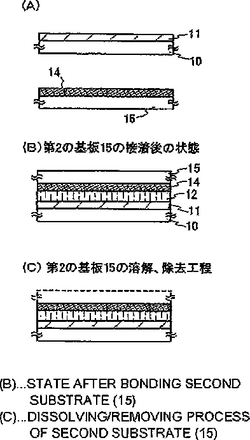

半導体装置および半導体装置の作製方法

(課題)様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)本発明は、基板上に被剥離層を形成し、この被剥離層にエッチングストッパー膜が設けられた封止基板を接着材で貼り合わせ、その後、封止基板のみをエッチングまたは研磨によって除去する。残ったエッチングストッパー膜は、そのままブロッキング膜として機能させる。また、貼り付ける部材としてマグネットシートを貼り付けてもよい。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 高い特性及び信頼性を有する半導体装置の作製方法を提供する。

【解決手段】 絶縁膜上の電極や配線形成後のドライエッチングにおけるエッチングダメージを防止する。ドライエッチングのプラズマによる荷電粒子の発生を、半導体層に達しないように、導電層を形成してダメージを抑制する。これにより、特に微細化な構造を持つ薄膜トランジスタにおいて、トランジスタ特性の劣化を生じさせない方法を提供することを目的とする。

(もっと読む)

3,201 - 3,220 / 3,316

[ Back to top ]