Fターム[5F110NN03]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935) | 複数層 (3,316)

Fターム[5F110NN03]に分類される特許

3,281 - 3,300 / 3,316

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】 電気光学装置において、他の不具合を発生させずに光リーク電流の発生を抑制し、高品位な表示を可能とする。

【解決手段】 基板上に、チャネル領域を有する半導体層を含んで構成された薄膜トランジスタと、薄膜トランジスタにより駆動される表示用電極と、半導体層の上層側及び下層側の少なくとも一方に積層された層間絶縁膜と、該層間絶縁膜の半導体層側とは反対側に積層された、チャネル領域を遮光するための遮光膜とを備えている。層間絶縁膜における半導体層とは反対側の表面には、チャネル領域のうち少なくともチャネル領域の縁部を遮光可能な領域において、半導体層に向かって局所的に窪んだ凹部が形成されている。遮光膜は、少なくとも凹部内に形成されている。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 第1絶縁膜を連続的に形成した後、第2絶縁膜を蒸着して薄膜トランジスタの半導体層とゲート絶縁膜を形成する薄膜トランジスタ及びその製造方法を提供する。

【解決手段】 薄膜トランジスタ及びその製造方法は、絶縁基板と、前記絶縁基板に連続的に形成され、パターニングされた多結晶シリコン層パターン105及び第1絶縁膜パターン106と、前記多結晶シリコン層パターン及び第1絶縁膜パターンが形成された基板上に形成された第2絶縁膜107と、前記第2絶縁膜上に形成されたゲート電極108、層間絶縁膜109及びソース/ドレーン電極110と、を含んでなる薄膜トランジスタ及びその製造方法であり、中間洗浄工程を略することができるため製造工程を短縮する効果がある。

(もっと読む)

光量検出回路およびそれを用いた表示パネル

【課題】 ダイオードによるフォトセンサはその構造上リフレッシュができず、光が当たっていない時のリーク特性が不安定であるため、フォトセンサには不適当である。また、薄膜トランジスタのフォトセンサは、光量は非常に微小なものであり、フィードバックが困難となる問題があった。

【解決手段】 薄膜トランジスタのフォトセンサに、出力電流を電圧に変換する検出回路を付加する。これにより微小な電流をフィードバックが可能な所望の範囲の電圧に変換できる。また、回路を構成する抵抗、容量、フォトセンサの接続数を変動させることによりフォトセンサの感度を変化させることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 薄膜トランジスタ特性を安定的に確保できる有機半導体薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】 本発明の一特徴による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成する段階、前記ゲート線上にゲート絶縁膜を形成する段階、前記ゲート絶縁膜上にデータ線及びドレイン電極を形成する段階、有機半導体を形成する段階、前記有機半導体を完全に覆う保護部材を形成する段階、前記保護部材、前記データ線、及び前記ドレイン電極の上に、前記ドレイン電極を少なくとも一部露出する接触孔を有する保護膜を形成する段階、並びに前記接触孔を通じて前記ドレイン電極と接続される画素電極を前記保護膜上に形成する段階を含む。

(もっと読む)

液晶装置及び電子機器並びに投射型表示装置

【課題】 アクティブマトリクス駆動方式の液晶装置において、プリチャージ回路、サンプリング回路等が有するTFTの下側からの戻り光等に対する遮光性能を高め、優れたスイッチング特性により高品質の画像表示を行う。

【解決手段】 液晶装置(200)は、一対の基板間に挟持された液晶層(50)と、基板にマトリクス状に設けられた画素電極(11)と、これをスイッチング制御するTFT(30)とを備える。このTFTや、プリチャージ回路(201)及びサンプリング回路(301)のTFTの下側には、遮光層が設けられている。

(もっと読む)

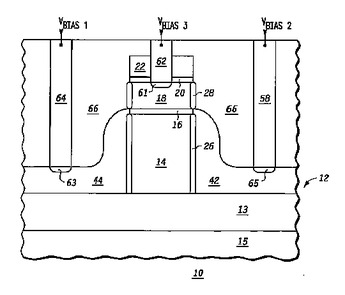

2つの制御領域を有する集積された電界効果トランジスタ、その使用、およびその製造方法

本発明は、特に、SOI技術およびサリサイド技術により、ダブルゲート・トランジスタ(10)として生成される、電界効果トランジスタ(10)に関する。トランジスタ(10)は、5ボルトよりも高いまたは9ボルトよりもさらに高いターンオン電圧に適し、非常に小さなチップ表面のみを必要とする。トランジスタ(10)は基板領域(14)を有する。基板領域(14)は、2つの電極領域(16、18)と、2つの電気的に絶縁性の絶縁層(100、102)であって、基板領域(14)の対向する面に配置され、制御領域(20、22)に隣接する、絶縁層と、少なくとも1つの電気的に絶縁性の領域(12、110)と、導電性の接続領域(28)、または、1つの電極領域(16)と該基板領域(14)との間の導電性の接続領域の部分(230)とに囲まれる。  (もっと読む)

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

ソース及びドレインの追加絶縁層を備えた共平面型薄膜トランジスタ

共平面型薄膜トランジスタ、TFT(22)及びその製造方法において、追加の絶縁層がソースコンタクト(30)及びドレインコンタクト(32)上に設けられ、当該追加の絶縁層の第1領域(34)がソースコンタクト(30)と実質的に同一領域を占有し、当該追加の絶縁層の第2領域(36)がドレインコンタクト(32)と実質的に同一領域を占有するように形が定められる。これにより、ゲート(62)−ソース容量、及びゲート(62)−ドレイン容量が低減される。一部の構成では、このことが追加のマスク又は形を定める工程なくして実現され得る。  (もっと読む)

(もっと読む)

可撓性電気光学装置及びその製造方法

本発明は、単結晶シリコン半導体を回路駆動部及び画素アレイの製造に用いる可撓性を有する高解像度液晶表示装置などの可撓性電気光学装置及びその製造方法に関する。本発明による可撓性電気光学装置は、可撓性単結晶層の上に電子素子が形成される素子層を備える可撓性下部基板部と、前記下部基板部に組み付けられた可撓性上部基板部と、前記下部基板部と前記上部基板部との間に配設された電気光学的物質層と、を備える。 (もっと読む)

接触部及びその製造方法、薄膜トランジスタ表示板及びその製造方法

【課題】低抵抗の導電物質からなる信号線を用いることにより、良好な接触特性を備える接触構造およびその製造方法を提供する。

【解決手段】接触部形成方法は、基板上に第1配線を形成する段階と、第1配線を覆い、第1配線の一部分を露出させるコンタクトホールを有する絶縁膜を形成する段階と、コンタクトホールによって露出する第1配線の表面に接触層を形成する段階と、接触層を介して第1配線と接続される第2配線を形成する段階とを含み、第1配線は、アルミニウムまたはアルミニウム合金で形成し、第2配線は、ITOまたはIZOで形成する。

(もっと読む)

ヘテロ接合を備える半導体デバイス

ヘテロ接合を有する半導体デバイス。このデバイスは、基板と少なくとも1つのナノ構造とを備える。この基板とナノ構造とは、異なる材料から成る。この基板は、例えばIV族半導体材料から成ることがあるのに対して、このナノ構造は、III−V族半導体材料から成ることもある。このナノ構造は、この基板によって支持され、この基板とエピタキシャルな関係にある。ナノ構造は、ゲートアラウンドトランジスタデバイスなどの電子デバイスの機能コンポーネントになる可能性がある。ゲートアラウンドトランジスタの一実施形態においては、ナノワイヤ(51)が、基板(50)によって支持され、この基板はドレインであり、このナノワイヤは電流チャネルであり、上部金属コンタクト(59)はソースである。薄いゲート絶縁膜(54)が、このナノワイヤとこのゲート電極(55A、55B)とを絶縁している。  (もっと読む)

(もっと読む)

高温電子素子

少なくともいくつかの実施例では、200℃を上回る温度での使用に適した電子素子は、炭化シリコン基板上に形成された集積回路と、厚い不活性化層とを有する。その他の実施例では、200℃を上回る温度での使用に適した電子素子は、サファイア基板上に配置されたシリコンから形成された集積回路と、厚い不活性化層とを有する。電子素子は、炭化水素掘削作業及び生産作業の関連で実装される。  (もっと読む)

(もっと読む)

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

分離領域を有する半導体デバイスを形成するための方法

分離構造を有する半導体デバイス(10)を形成するための方法が漏れ電流を低減する。チャネル分離構造(32、30、34)がチャネル構造の中の漏れ電流を低減する。さらに、電流電極領域の下に電流電極誘電体分離構造(36)が形成され、電流電極(40)間の漏れを防ぐ。  (もっと読む)

(もっと読む)

薄膜トランジスタの封止方法

ゲート電極と、ゲート誘電体と、ソースおよびドレイン電極と、半導体層とを含む薄膜トランジスタを提供する工程と、封止材料をアパーチャマスクのパターンを通して前記半導体層の少なくとも一部の上に蒸着する工程とを含む、薄膜トランジスタの封止方法。  (もっと読む)

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

3,281 - 3,300 / 3,316

[ Back to top ]