Fターム[5F110NN36]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 製法 (8,383) | 堆積 (7,357) | スピンオン塗布 (1,199)

Fターム[5F110NN36]に分類される特許

141 - 160 / 1,199

膜形成用組成物および該組成物を用いた薄膜トランジスタ

【課題】 本発明の目的は、有機半導体素子の製造プロセス適応性に優れる膜形成用組成物および該組成物を用いた薄膜トランジスタを提供することである。

【解決手段】上記課題は、必須成分として、(a)式(I)で表される構造を0.6mmol/g以上含有する有機化合物と、(b)有機溶剤とを含有する膜形成用組成物および該組成物を有機半導体素子の絶縁膜等に用いる薄膜トランジスタにより達成される。該薄膜トランジスタは、閾値電圧が高く、ON/OFF電流比も高い特性の良好なトランジスタとなる。

【化1】 (もっと読む)

(もっと読む)

薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法

【課題】TFT特性が良好で表示品質や回路配線の層間絶縁性を確保できるTFTアレー基板の製造方法等を提供する。

【解決手段】基材1上への酸化物半導体膜3のパターン形成工程、酸化物半導体膜へのソース電極接続領域3s及びドレイン電極接続領域3dの形成工程、酸化物半導体膜を覆うゲート絶縁膜4の形成工程、ゲート絶縁膜にコンタクトホールを開けてソース電極6s及びドレイン電極6dをソース電極接続領域及びドレイン電極接続領域に接続するとともに酸化物半導体膜上にゲート絶縁膜を介してゲート電極7を形成し、第1回路配線群17を形成する工程、ソース電極、ドレイン電極、ゲート電極及び第1回路配線群上に層間絶縁膜18を形成する工程、層間絶縁膜上に第2回路配線群19を形成する工程を有し、ゲート絶縁膜4の厚さを100nm〜500nmの範囲とし、層間絶縁膜18の厚さを1μm以上且つゲート絶縁膜4の2倍〜10倍の厚さとする。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

EL表示装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

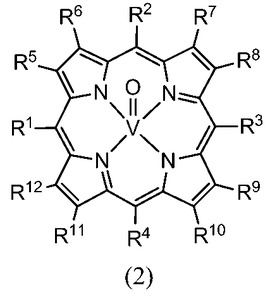

テトラビシクロポルフィリンバナジル錯体の製造方法、半導体層形成用組成物、電子デバイスの製造方法、太陽電池及び太陽電池モジュール

【課題】電子デバイスで好適に用いられるテトラベンゾポルフィリンバナジル錯体の高純度製造法の提供。

【解決手段】テトラビシクロポルフィリン化合物とバナジル化合物の反応を65℃以上95℃以下の温度で行う。式(2)の錯体の製造方法。 (もっと読む)

(もっと読む)

レーザ照射装置

【課題】小型のレーザ照射装置で光干渉がなく、連続した結晶成長を実現することである。

【解決手段】メガヘルツレーザビームを用い、分割したレーザビームを半導体膜に照射して、半導体膜を結晶化する。その際に分割ビームに光路差を設けて光干渉を抑える。光路差はメガヘルツレーザビームのパルス幅に相当する長さ以上、パルス発振間隔に相当する長さ未満に設定され、非常に短い光路差で光干渉を抑えることができる。そのためレーザのエネルギー劣化がなく効率的に且つ連続的にレーザビームを照射することができる。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

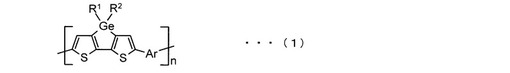

ジチエノゲルモール重合体及びそれを含有した有機半導体デバイス

【課題】耐久性及び半導体特性の安定性に優れた有機半導体材料として有用である熱安定性の高いジチエノゲルモール重合体、及びそれを含有する有機半導体材料より形成される有機半導体デバイスを提供する。

【解決手段】ジチエノゲルモール重合体は、下記化学式(1)

【化1】

(式中、R1及びR2はそれぞれ独立して置換基を有してもよい炭素数1〜20の炭化水素基であり、Arは置換基を有してもよい2価の芳香環と、芳香環数2〜7の置換基を有してもよい2価の多核芳香環と、置換基を有してもよい2価の芳香環及び/又は芳香環数2〜7の置換基を有してもよい2価の多核芳香環を複数連結させた2価のアリーレン基とから選ばれる何れかであり、nは少なくとも2の正数)で示されるものである。有機半導体デバイスは、このジチエノゲルモール重合体を有機半導体層とするものである。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

画素アレイ基板構造、画素アレイ基板構造の製造方法、表示装置、及び、電子機器

【課題】画品位に影響を及ぼす、2層目の平坦化膜のコンタクト部を自由にレイアウトできるようにする。

【解決手段】回路部が形成された基板表面を平坦化するための平坦化膜を、基板上に順に積層された第1,第2の平坦化膜74,77からなる2層構造とする。そして、第1,第2の平坦化膜74,77間に中継配線76を形成し、この中継配線76によって、第1の平坦化膜74に形成され、トランジスタ(TFT)72を含む回路部に接続された第1のコンタクト部75と、第2の平坦化膜77の第1のコンタクト部75と平面視で異なる位置に形成された第2のコンタクト部75とを電気的に接続する。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を作製し、提供することを課題の一とする。

【解決手段】薄膜トランジスタの酸化物半導体層を覆う絶縁層にボロン元素またはアルミ

ニウム元素を含ませる。ボロン元素またはアルミニウム元素を含む絶縁層は、ボロン元素

またはアルミニウム元素を含むシリコンターゲットまたは酸化シリコンターゲットを用い

るスパッタ法により形成する。また、ボロン元素に代えてアンチモン元素(Sb)やリン

元素(P)を含む絶縁層で薄膜トランジスタの酸化物半導体層を覆う構成とする。

(もっと読む)

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】オフ電流が低減できる半導体装置及び半導体装置を提供する。

【解決手段】絶縁表面上に形成され、ソース領域、ドレイン領域、及びチャネル形成領域を含む単結晶半導体層と、単結晶半導体層を覆うゲート絶縁膜と、ゲート絶縁膜を介して、チャネル形成領域に重畳するゲート電極と、ソース領域に接続されるソース電極と、ドレイン領域に接続されるドレイン電極と、を有し、ソース領域及びドレイン領域のうち、少なくともドレイン領域は、チャネル形成領域に隣接する第1の不純物領域と、第1の不純物領域に隣接する第2の不純物領域と、を含み、第1の不純物領域の深さ方向の不純物濃度分布の極大は、第2の不純物領域の深さ方向の不純物濃度分布の極大よりも絶縁表面側にあり、ドレイン電極は、ドレイン領域に含まれる第2の不純物領域の一部と接続する半導体装置を提供する。

(もっと読む)

141 - 160 / 1,199

[ Back to top ]