Fターム[5F110PP04]の内容

Fターム[5F110PP04]に分類される特許

21 - 40 / 686

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

半導体装置

【課題】動作特性および信頼性の向上した、新規なマルチゲート構造のトランジスタを提

供することを課題とする。

【解決手段】2つ以上のゲート電極と、直列に接続した2つ以上のチャネル形成領域、ソ

ース領域、ドレイン領域、及び高濃度不純物領域を有する半導体層と、を有するマルチゲ

ート構造のトランジスタにおいて、ソース領域側に近接するチャネル形成領域のチャネル

長が、ドレイン領域側に近接するチャネル形成領域のチャネル長よりも大きくする。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

未焼結シリコン粒子膜及び半導体シリコン膜、並びにそれらの製造方法

【課題】本発明は、新規な未焼結シリコン粒子膜及び半導体シリコン膜、並びにそれらの製造方法を提供する。

【解決手段】本発明の未焼結シリコン粒子膜130は、互いに未焼結のシリコン粒子からなり、且つ不活性ガス雰囲気中において1気圧の圧力及び600℃の温度で加熱したときに脱離する脱離性ガスの量が、未焼結シリコン粒子膜の質量に基づいて、500質量ppm以下である。未焼結シリコン粒子膜を製造する本発明の方法は、(a)シリコン粒子分散体を、基材上100に塗布して、シリコン粒子分散体膜110を形成する工程、(b)シリコン粒子分散体膜110を乾燥して、乾燥シリコン粒子膜120を形成する工程、及び(c)乾燥シリコン粒子膜120を焼成することによって、未焼結シリコン粒子膜130を形成する工程を含む。本発明の半導体シリコン膜140は、互いに焼結されているシリコン粒子からなり、且つ炭素原子を実質的に含有していない。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体シリコン膜及び半導体デバイス、並びにそれらの製造方法

【課題】本発明の目的は、新規な半導体シリコン膜及びそのような半導体シリコン膜を有する半導体デバイス、並びにそれらの製造方法を提供することである。

【解決手段】本発明の半導体シリコン膜(160)は、複数の細長シリコン粒子(22)が短軸方向に隣接してなる半導体シリコン膜である。ここでは、細長シリコン粒子(22)は、複数のシリコン粒子の焼結体である。また、このような半導体シリコン膜(160)を製造する本発明の方法は、第1のシリコン粒子分散体を、基材(100)上に塗布し、乾燥し、光(200)を照射して、第1の半導体シリコン膜(130)を形成する工程、第2のシリコン粒子分散体を、第1の半導体シリコン膜(130)に塗布し、乾燥し、光(200)を照射する工程を含む。ここで、この方法では、第1のシリコン粒子分散体の第1のシリコン粒子の分散が5nm2以上である。

(もっと読む)

半導体装置の作製方法、および半導体装置

【課題】低温プロセスを実現する半導体装置の作製方法、及び半導体装置を提供する。

【解決手段】結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、一部の上層部分を非晶質化するとともに、一部の下層部分に結晶質を残存させ、加熱処理を行うことによって、一部の中の水素を拡散させる。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

表示装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

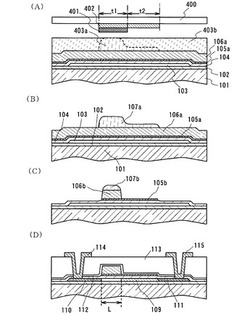

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

半導体装置の作製方法

【課題】 光学系を複雑化させることなく、均一なエネルギー密度のレーザ光を被照射体

に照射することができる、レーザ照射装置の提案を課題とする。

【解決手段】本発明のレーザ照射装置は、レーザ発振器と、被照射体の表面における一軸方向に、前記レーザ発振器から発振されたレーザ光によって形成されるビームスポットを繰り返し走査するための光学系と、前記表面において前記一軸方向と交差する方向に向かって、前記レーザ光に対する前記被照射体の相対的な位置を移動させるための位置制御手段とを有することを特徴とする。

(もっと読む)

21 - 40 / 686

[ Back to top ]