Fターム[5F110PP04]の内容

Fターム[5F110PP04]に分類される特許

41 - 60 / 686

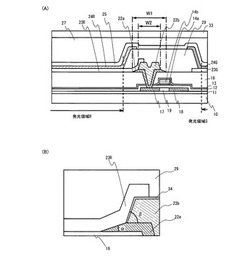

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いて、トランジスタのしきい値電圧を変化させる。

【解決手段】第1のチャネル形成領域を有する第1の半導体層と、第2のチャネル形成領域を有する第2の半導体層に対して、それらの上に形成された薄膜の応力を用いて、トランジスタのしきい値電圧を異ならせることができる。これらを電気的に接続することで、E/D MOS回路を提供できる。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】第1の半導体層に設けられた第1のゲート電極と、第2の半導体層に設けられた第2のゲート電極と、第1の半導体層と第2の半導体層に接して設けられた第1の絶縁層と、第1の絶縁層が設けられた第1の半導体層の一方の面の反対側に設けられた第2の絶縁層と、第1の絶縁層が設けられた第2の半導体層の一方の面の反対側に設けられた第2の絶縁層及び第3の絶縁層と、を有し、第1の半導体層には第2の絶縁層により応力が加わり、第2の半導体層には第2の絶縁層と第3の絶縁層により応力が加わることで、第1の半導体層及び第2の半導体層に加わる応力が異なる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

放射線撮像装置、放射線撮像表示システムおよびトランジスタ

【課題】被曝量による閾値電圧のシフトを抑制するが可能なトランジスタを提供する。

【解決手段】放射線撮像装置1は、フォトダイオードとトランジスタ111Bとを含む光電変換層を有する。トランジスタ111Bは、基板11上に、第1ゲート電極120A、第1ゲート絶縁膜129、半導体層126、第2ゲート絶縁膜130および第2ゲート電極120Bをこの順に有し、第1ゲート絶縁膜129および第2ゲート絶縁膜130におけるSiO2膜の総和が65nm以下となっている。トランジスタが被曝すると、ゲート絶縁膜におけるSiO2膜に正孔がチャージされ、閾値電圧がシフトし易くなるが、上記のようなSiO2膜厚の最適化により、閾値電圧シフトが効果的に抑制される。

(もっと読む)

半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。また、本発明の目的は、基材がポリマー材料を有する半導体積層体を提供することである。

【解決手段】半導体積層体(110)を製造する本発明の方法は、(a)基材上にシリコン粒子分散体膜を形成する工程、(b)シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び(c)未焼結半導体シリコン膜に光を照射して、半導体シリコン膜を形成する工程を含む。また、本発明の半導体積層体(110)は、基材(112)及び半導体シリコン膜(118)を有し、基材が、ポリマー材料を有し、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である。

(もっと読む)

表示装置

【課題】本発明は、アクティブマトリクス型表示装置の製造コストを低減するこ

とを課題とし、安価な表示装置を提供することを課題とする。また、本発明の表

示装置を表示部に用いた安価な電子装置を提供することを目的とする。

【解決手段】 アクティブマトリクス型表示装置の製造コストを低減するために

画素部に用いるTFTを全て一導電型TFT(ここではpチャネル型TFTもし

くはnチャネル型TFTのいずれか一方を指す)とし、さらに駆動回路もすべて

画素部と同じ導電型のTFTで形成することを特徴とする。これにより製造工程

を大幅に削減し製造コストを低減することが可能となる。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけられた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとして機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面を有するディスプレイを実現するものである。

(もっと読む)

発光装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】高性能な電気特性を実現しうるpoly−Si膜の結晶性分布を有した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、絶縁性の基板と、前記絶縁性基板の上に形成されたゲート電極と、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜の上に形成された結晶シリコン膜と、前記結晶シリコン膜の端部の上方に形成されたソース電極と、前記結晶シリコン膜における前記ソース電極が形成された端部と対向する端部の上方に形成され、前記ソース電極と離間しているドレイン電極とを具備する薄膜トランジスタにおいて、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されている前記結晶シリコン膜の端部から、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されていない前記結晶シリコン膜の中央部に向かって、前記結晶シリコン膜の結晶化率が小さくなっている。

(もっと読む)

レーザ照射方法及びレーザ照射装置

【課題】光学調整に困難を伴うことなく、3以上のレーザビームを照射面にて合成し、高出力で生産性を向上させることができるレーザを照射する技術の提供。

【解決手段】その技術は、波長の互いに異なるレーザ発振器とダイクロイックミラー、又はそれに加えて偏光子を用いてレーザビームを合成し、高出力で生産性を向上させレーザを照射するものであり、例えばレーザ発振器から射出されたレーザ光1をダイクロイックミラー1を通過させ、レーザ光1とは波長の異なるレーザ発振器から射出されたレーザ光2をダイクロイックミラー1で反射させてレーザ光を合成し、合成されたレーザ光を照射レーザ光とし、照射レーザ光を照射面上に投影するものである。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】絶縁層上に結晶性の良好な半導体層を形成することができる、半導体装置の製造方法を提供する。

【解決手段】絶縁層41上に厚さ4nm〜1μmの非晶質の半導体層43を形成する工程と、この半導体層43に対して、波長が350nm〜500nmの範囲内のエネルギービームを照射することにより、半導体層43を結晶化させる工程とを含んで、半導体装置を製造する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去電圧を低減させることができる半導体記憶装置を提供することを課題とする。

【解決手段】チャネル形成領域を有する半導体膜と、半導体膜のチャネル形成領域上に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極材料には、半導体基板よりも仕事関数があまり大きくならない窒化チタンとすることにより、消去電圧低減を図ったものである。なお、上記窒化チタンのチタン組成比は、低消費電力化及び誤書き換え耐性の観点から56atomic%以上75atomic%以下がよい。

(もっと読む)

半導体装置の製造方法

【課題】多結晶シリコン層の表面平坦性を向上できる半導体装置の製造方法を提供する。

【解決手段】本実施形態によれば、半導体装置の製造方法は、基板上に非晶質シリコン膜を形成する工程と、前記非晶質シリコン膜を結晶化して多結晶シリコン膜を形成する工程と、プラズマドーピング法を用いて、前記多結晶シリコン膜にイオンを注入する工程と、前記イオンを注入した前記多結晶シリコン膜の表面を研磨する工程と、を備える。

(もっと読む)

半導体装置

【課題】非晶質上に低コストで高性能な半導体装置を形成する技術を提供する。

【解決手段】GeがSi濃度よりも高濃度に含まれた疑似Ge領域(2)を含有し、該領域のGe濃度は初期SiGe薄膜中のGe濃度よりも高濃度であり、リボン形状をした結晶粒(1)は、互いに平行で且つ直線状に配置している疑似Ge領域(2)に挟まれる構造を有し、結晶粒(1)内においてGe濃度はSi濃度よりも低濃度であり、且つ結晶粒(1)内のGe濃度は初期SiGe薄膜中のGe濃度よりも低濃度であり、さらに各々の結晶粒(1)は相互に同一の方位を有する結晶粒から成っていることを特徴とする非晶質上の半導体薄膜からなる半導体装置。

(もっと読む)

41 - 60 / 686

[ Back to top ]