Fターム[5F110QQ24]の内容

薄膜トランジスタ (412,022) | 製造工程一般 (15,099) | ダングリングボンドの終端化(例;水素化) (1,179) | 拡散 (1,072) | 気相拡散(雰囲気中) (603)

Fターム[5F110QQ24]の下位に属するFターム

プラズマ雰囲気中 (288)

Fターム[5F110QQ24]に分類される特許

301 - 315 / 315

半導体装置の製造方法

【課題】 大気中に曝すことなく不純物元素の混入を防ぎ、かつフラットバンド電圧のバラツキを抑えるための半導体装置の製造方法を提供する。

【解決手段】 大気に曝すことなく半導体膜(105)を酸素プラズマ(106)で表面処理する第1工程(D)、第1工程に続き大気に曝すことなく、表面処理された半導体膜(105)上にゲート絶縁膜(107)を形成する第2工程(E)を備えたことを特徴とする。大気に曝さず酸素プラズマ処理をすることにより、フラットバンド電圧を実質0Vにし、フラットバンド電圧のバラツキを抑え、フラットバンド電圧のシフトを防止することができるようになった。

(もっと読む)

表示装置及びその作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する表示装置の作製方法を提供する。

【解決手段】 本発明の表示装置の一は、絶縁表面上に設けられたソース電極層、ドレイン電極層及び画素電極層を有し、ソース電極層及びドレイン電極層上に一導電型を有する半導体層を有し、一導電型を有する半導体層上に結晶性半導体層を有し、結晶性半導体層に接してゲート絶縁層を有し、ゲート絶縁層に接してゲート電極層を有し、ゲート絶縁層、ゲート電極層、及び画素電極層上に絶縁層を有し、ゲート絶縁層及び絶縁層は、ソース電極層またはドレイン電極層に達する第1の開口部、及び画素電極層に達する第2の開口部を有し、第1の開口部及び第2の開口部に、ソース電極層またはドレイン電極層と画素電極層とが電気的に接続する配線層を有する。

(もっと読む)

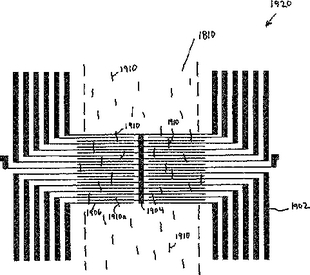

大面積ナノ可能マクロエレクトロニクス基板およびその使用

複数の半導体デバイスを有する電子的な基板を得るための方法および装置が、説明される。ナノワイヤ薄膜が、基板上に形成される。ナノワイヤ薄膜は、動作電流レベルを達成するのに十分なナノワイヤの密度を有するように形成される。複数の半導体領域が、ナノワイヤ薄膜に画定される。コンタクトが、半導体デバイス領域において形成され、それによって、電気的な接続を複数の半導体デバイスに提供する。さらに、ナノワイヤを製造するための様々な材料、p型ドーピングナノワイヤおよびn型ドーピングナノワイヤを含む薄膜、ナノワイヤヘテロ構造、発光ナノワイヤヘテロ構造、ナノワイヤを基板上に配置するためのフローマスク、ナノワイヤを成膜するためのナノワイヤ噴霧技術、ナノワイヤにおける電子のフォノン散乱を減少または除去するための技術、および、ナノワイヤにおける表面準位を減少させるための技術が、説明される。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 高い特性及び信頼性を有する半導体装置の作製方法を提供する。

【解決手段】 絶縁膜上の電極や配線形成後のドライエッチングにおけるエッチングダメージを防止する。ドライエッチングのプラズマによる荷電粒子の発生を、半導体層に達しないように、導電層を形成してダメージを抑制する。これにより、特に微細化な構造を持つ薄膜トランジスタにおいて、トランジスタ特性の劣化を生じさせない方法を提供することを目的とする。

(もっと読む)

薄膜半導体装置の製造方法および薄膜半導体装置

【課題】水蒸気アニールによる半導体薄膜の処理を行う場合であっても導電型によらずにしきい値電圧を確保できる薄膜トランジスタの製造方法および薄膜トランジスタを提供する。

【解決手段】基板31上にTFT40、43を形成し、これらを覆う状態で少なくとも最下層を構成する膜中に水酸基が含有されない層間絶縁膜40を形成する。その後、水分雰囲気中において熱処理を行うことによりTFT40、43を構成する半導体薄膜34のダングリングボンドに酸素または水素を結合させると共に、層間絶縁膜40の緻密化を図る。層間絶縁膜40は、例えば窒化シリコンからなる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 半導体層上にゲート絶縁膜を介して設けられたゲート電極を有する薄膜トランジスタの製造方法において、半導体層及びゲート絶縁膜間の界面特性を改善する安価な薄膜トランジスタの製造方法を得ること。

【解決手段】 本方法は、絶縁性の基板上に前記半導体層を成膜する工程(1A)と、重水素を含む雰囲気で熱処理を行ない、前記半導体層に第1の酸化膜を形成する工程(1B)と、プラズマCVD法を利用して、前記第1の酸化膜上に第2の酸化膜を形成する工程(1C)と、前記第2の酸化膜上に前記導電層を形成する工程(2E)とを有する。前記熱処理の温度は、前記薄膜トランジスタのソース及びドレイン領域を活性化する際の熱処理の温度に実質的に等しい。

(もっと読む)

レーザ照射方法及びレーザ照射装置、並びに非単結晶を結晶化する方法及び半導体装置を作製する方法

【課題】 光学調整に困難を伴うことなく、3以上のレーザビームを照射面にて合成し、高出力で生産性を向上させることができるレーザを照射する技術の提供。

【解決手段】 その技術は、波長の互いに異なるレーザ発振器とダイクロイックミラー、又はそれに加えて偏光子を用いてレーザビームを合成し、高出力で生産性を向上させレーザを照射するものであり、例えばレーザ発振器から射出されたレーザ光1をダイクロイックミラー1を通過させ、レーザ光1とは波長の異なるレーザ発振器から射出されたレーザ光2をダイクロイックミラー1で反射させてレーザ光を合成し、合成されたレーザ光を照射レーザ光とし、照射レーザ光を照射面上に投影するものである。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する半導体装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な半導体装置の作製方法を提供する。

【解決手段】 本発明は、非晶質半導体膜に触媒元素を添加し加熱して結晶性半導体膜を形成し、該結晶性半導体膜に5族元素(15族元素)を有する半導体膜または希ガス元素

を有する半導体膜を形成し加熱して、触媒元素を結晶性半導体膜から除去した後、逆スタガ型TFTを形成することを特徴とする。

(もっと読む)

レーザ処理装置、レーザ照射方法、及び半導体装置の作製方法

【課題】 レーザ照射時の振動の発生を抑制し、一様なエネルギープロファイルを持つレーザビームを一方向に移動させることにより、信頼性のよい半導体装置を短時間で量産する。

【解決手段】 円柱状の回転体の表面に、回転体の曲率に沿って基板を回転体表面に吸着させ、回転体を回転させ、基板上に成膜された半導体膜を一度にレーザ照射する。また、回転体の回転軸方向に移動機構を設け、回転体が1回転したときに照射位置をずらすようにする。または回転体を回転させながら回転軸方向に移動させることも可能である。

(もっと読む)

レーザ光を照射する方法及び装置、並びに非単結晶半導体膜をアニールする方法及び半導体装置を作製する方法

【課題】 レンズアレイを用いて結晶化等を行う際に照射体において反射した戻り光による悪影響を回避した、レーザ発振器の安定性を高く保ち、かつ均一なレーザ処理をすることができるレーザ照射技術、並びにそれを用いる結晶化方法及び半導体装置の作製方法の提供。

【解決手段】 レーザ発振器から射出されたレーザ光をシリンドリカルレンズアレイ等のレンズアレイを通過させて複数に分割し、分割後のレーザ光を焦点を結ぶ位置でスリットの開口を通過させ、その後更に集光レンズを通過させて照射面上に照射する。

このようにして、スリットを用いることにより照射体で反射した戻り光をカットし、レーザの出力又は周波数の変動や、ロッドの破壊を防ぐものであり、その結果レーザ光の出力を安定化させ、これによって、安定して強度分布の均一なレーザ光を照射面において照射することができ、均一なアニールを行う。

(もっと読む)

半導体装置の作製方法

【課題】 ナノインプリント法を用いることでコストを抑えることができる、半導体装置の作製方法の提案を課題とする。

【解決手段】 本発明は、島状の半導体膜上にゲート絶縁膜と、導電膜と、レジストとを順に形成し、パターンが形成されたモールドをレジストに押し付けた状態でレジストの硬化を行なうことで、パターンをレジストに転写し、導電膜の一部が露出するまでパターンが転写されたレジストの表面をアッシングし、アッシングされたレジストをマスクとして用い、導電膜をエッチングすることを特徴とする。

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

301 - 315 / 315

[ Back to top ]