Fターム[5F140AA38]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | ESD対策 (155)

Fターム[5F140AA38]に分類される特許

1 - 20 / 155

半導体装置

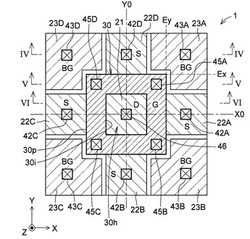

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置

【課題】LDMOSトランジスタのESD耐量の改善を図る。

【解決手段】ゲート電極5とレジストマスクによりP型ベース層2に、中心部に複数の開口部7を有するラダー形状のN+型ソース層3を形成する。開口部7に該開口部7を埋設するP+型コンタクト層4を形成する。このとき、開口部7の端部、即ちP+型コンタクト層4の端部からN+型ソース層3の端部までの距離を所定の距離にする。所定の距離とは該距離の増加と共に増大するLDMOSトランジスタのHBM+耐量が飽和し始める距離である。

(もっと読む)

半導体装置、およびその製造方法

【課題】従来に比して高いESD耐量性能を有するESD保護回路を備えた半導体装置、およびその製造方法を提供する。

【解決手段】内部回路に用いられる第1の半導体素子と、静電気による内部回路の破壊を抑制するESD保護回路として用いられる第2の半導体素子とを備える半導体装置の製造方法であって、基板に第1の半導体素子および第2の半導体素子各々についての端子領域層を形成する端子領域層形成ステップと、基板上の前記第2の半導体素子の端子領域層を除く領域について結晶欠陥を形成させる処理を施す欠陥形成ステップと、金属膜を第1の半導体素子および第2の半導体素子各々の端子領域層表面に形成する金属膜形成ステップと、金属膜と、第1の半導体素子および第2の半導体素子各々の端子領域層とをシリサイド化するシリサイド化ステップとを含む、半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

静電気保護用のMOS型半導体装置

【課題】ESD素子のESD耐量を向上させる。

【解決手段】ESD素子21は半導体基板1表面に形成したP型ウェル領域2上にゲート絶縁膜を介して、一方向に延びた複数本のゲート電極3が相互に平行に設けられており、P型ウェル領域2の表面におけるゲート電極3の直下域がチャネル領域9になっている。そして、チャネル領域9間の領域がN+ソース領域5又はN+ドレイン領域4となっており、N+ソース領域5とN+ドレイン領域4とは交互に配列されている。そして、並列して隣接するゲート電極3間に位置するN+ドレイン領域4を分割し、かつ隣接するゲート電極3を接続するようにゲート電極接合領域10を設ける。なお、ゲート電極接合領域10の直下域にはチャネル領域9と同一の不純物濃度を有する領域11が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】静電保護素子である保護トランジスタのサイズを縮小することができ、ゲート端子の抵抗成分を同程度に抑え、時定数を増加させることなく、保護トランジスタの回路動作スピードの低下を防ぐことができるとともに、電荷集中を緩和し、静電破壊耐量を向上させることができる。

【解決手段】本発明に係る半導体装置は、ソース・ドレイン領域と、ソース・ドレイン領域の上方に形成されたゲート電極と、ゲート電極の側面に形成されたサイドウォールと、ソース・ドレイン領域の上面に、サイドウォールから所定の距離だけ離間して形成された第1のシリサイド膜と、ゲート電極の上面に、サイドウォールから所定の距離だけ離間して形成された第2のシリサイド膜とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生サイリスタの動作による破壊が生じない半導体装置及びその製造方法を提供する。

【解決手段】少なくともドレイン側p+層及びn+層のうちの、ボディ領域の導電型と同一型の層の下方において当該層と対向して半導体層の内部に形成された調整層を含む半導体装置。少なくともドレイン側p+層及びn+層のうちの、ボディ領域の導電型と同一型の層の下方において当該層と対向して半導体層の内部に調整層を形成する調整層形成ステップを含む半導体装置製造方法。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域501を有するESD保護用のN型MOSトランジスタにおいて、ESD保護用のN型MOSトランジスタのゲート電極301下面のゲート絶縁膜を介してP型シリコン基板表面に形成されたチャネル領域の表面に、ESD保護用のN型MOSトランジスタのドレイン領域202から一定の距離を隔てたオフセット領域601を介して、濃いP型の不純物濃度領域からなるP型ブレークダウン領域401を形成した半導体装置とした。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域を有するESD保護用のN型MOSトランジスタにおいて、前記ESD保護用のN型MOSトランジスタのドレイン領域の一部分のみが前記ESD保護用のN型MOSトランジスタのゲート絶縁膜を介して前記ESD保護用のN型MOSトランジスタのゲート電極と重なり合う重畳部を形成する半導体装置とした。

(もっと読む)

1 - 20 / 155

[ Back to top ]