Fターム[5F140AC02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 空乏層制御型(ディプレッション型) (42)

Fターム[5F140AC02]に分類される特許

21 - 40 / 42

電界効果トランジスタ

【課題】単位ゲート幅あたりのドレイン容量を低減できる電界効果トランジスタを提供する。

【解決手段】チャネル形成領域を有する第1導電型の第1半導体領域14に、4つの辺を有する矩形環状のゲート電極21(G)が形成され、ゲート電極の内側にドレイン領域18D(D)が形成され、4つの辺の外側の領域のそれぞれにおいて、対応するドレイン領域のチャネル幅を狭めない幅でソース領域18S(S)が形成され、即ち、矩形形状のドレイン領域の四辺全てにゲート電極が形成され、トランジスタが構成されている構成とする。

(もっと読む)

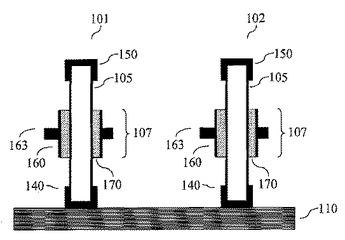

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

高圧バイポーラCMOS−DMOS集積回路装置およびこれを形成するためのモジュール式方法

エピタキシャル層を含まない基板においてさまざまな半導体装置を製造するために全低温プロセスが用いられる。装置は分離されていないラテラルDMOS、分離されていない拡張されたドレインまたはドリフトされたMOS装置、ラテラルトレンチDMOS、分離されたラテラルDMOS、JFETおよび空乏モード装置、ならびにP−Nダイオードクランプおよびレクチファイヤおよび接合端子を含む。プロセスが高温処理の必要をなくし、「注入されたままの」ドーパントプロファイルを使用するので、残りの装置を生成するのに使用されるプロセスを変更する必要なしに、装置がICに加えられたり省略されたりすることを可能にするモジュール式アーキテクチャを構成する。  (もっと読む)

(もっと読む)

半導体素子、半導体素子の製造方法

【課題】製造プロセスにおけるゲート電極への帯電に起因するチャージアップを防ぐことが可能な半導体素子を提供する。

【解決手段】半導体基板内に形成されたn型の不純物からなるソース領域4と、半導体基板内に形成されたn型の不純物からなるドレイン領域5と、ソース領域4及びドレイン領域5間の半導体基板上にゲート絶縁膜3を介して形成されたゲート電極6とを含むMOSトランジスタを有する半導体素子であって、半導体基板内に形成されたn型の不純物領域7と、半導体基板内に形成されたp型の不純物領域10と、n型の不純物領域7及びp型の不純物領域11の各々とゲート電極6とを接続するために設けられた配線H1及びH2とを備える。

(もっと読む)

複合半導体装置

【課題】HEMTとダイオードとから成る複合半導体装置の小型化が要求されている。

【解決手段】本発明に従うHEMTとダイオードとから成る複合半導体装置は、電子走行層3と電子供給層4とを含む半導体領域5と、この一方の主面上に形成されたソース電極7及びドレイン電極8とゲート電極12とを有し、更に、半導体領域5の一方の主面上におけるゲート電極12とドレイン電極8との間にショットキー電極60を有する。ショットキー電極60は導体60aによってソース電極7に接続されている。ショットキー電極60と半導体領域5とで形成されたショットキーダイオードは、帰還又は回生又は保護ダイオードとして機能する。このショットキーダイオードの電流はゲート電極12に基づく空乏層に妨害されない。

(もっと読む)

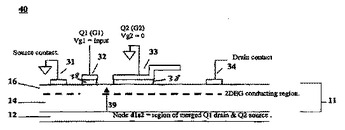

併合ゲートカスコードトランジスタ

この発明の実施例に従う併合ゲートトランジスタは、半導体要素と、半導体要素の上面に電気的に接続された供給電極と、半導体要素の上面に電気的に接続され、かつ、供給電極から横方向に間隔をあけたドレイン電極と、供給電極およびドレイン電極の間に位置決めされ、かつ、半導体要素に容量結合されて、トランジスタの第1の部分を形成する第1のゲートと、第1のゲートに隣接して供給電極およびドレイン電極の間に位置決めされて、トランジスタの第2の部分を形成する第2のゲートとを含み、第2のゲートも半導体要素に容量結合される。第1のゲートは、第1の部分の導通が入力電圧信号の値に基づくように入力電圧信号に接続され、第2のゲートは、所定の定電圧とソース電極における電圧との間の電圧差が所定のレベルに達するまでトランジスタの第2の部分が導通するように所定の定電圧に接続される。  (もっと読む)

(もっと読む)

AlN障壁層を有するGaN系電界効果トランジスタ、及びそのような電界効果トランジスタの製造方法

【課題】 本発明は、高出力、高耐圧、高速、高周波化などを達成し得る新規なGaN系ヘテロ接合トランジスタを提供することを目的とする。

【解決手段】上記課題は、GaN又はInGaNからなるチャネル層(4)と、AlNからなる障壁層(5)と含むヘテロ界面を構成する層と、トランジスタ素子表面に形成された絶縁膜(9)を有する電界効果トランジスタ(1)、特に絶縁膜としてSiN絶縁膜を用いた電界効果トランジスタや、そのような電界効果トランジスタの製造方法によって解決される。

(もっと読む)

半導体装置及びその製造方法

【課題】 ディプリーション型MOSトランジスタのパターン面積を増大させずに、その抵抗を大きくする。

【解決手段】 半導体基板1上にイオン注入することでチャネル領域となる低濃度不純物領域3を形成する。次に、ゲート絶縁膜4及びゲート電極5を形成する。次に、半導体基板1の全面に層間絶縁膜6を形成し、その後当該層間絶縁膜6を選択的にエッチングし、ソース形成領域及びドレイン形成領域をそれぞれ一部露出させるコンタクトホール7を形成する。次に、コンタクトホール7を介してイオン注入・熱処理(アニーリング)し、ソース領域8及びドレイン領域9を形成する。ソース領域8及びドレイン領域9はゲート電極5とオーバーラップせず、ゲート電極5の端部から数μm以上(例えば、3μm)離間して形成されている。

(もっと読む)

応力変形させた半導体装置およびその製造方法

【課題】応力を調整し、性能向上を図った半導体装置、およびその製造法を提供すること。

【解決手段】ゲート電極104は、半導体基板(バルクシリコン基板、SOI層など)102から電気的に絶縁されている。第1側壁スペーサ110がゲート電極104の側壁に沿って形成される。上記犠牲側壁スペーサが第1側壁スペーサ110と隣接するように形成される。上記犠牲側壁スペーサおよび第1側壁スペーサ110は半導体基板102を覆っている。平坦化層は、該平坦化層の一部が上記犠牲側壁スペーサと隣接するように、半導体基板102を覆って形成されている。上記犠牲側壁スペーサが取り除かれ、エッチングによって半導体基板102内にくぼみが形成される。実質的に、上記くぼみは第1側壁スペーサ110と上記平坦化層の一部との間に配置されている。半導体材料(SiGe、SiCなど)116は上記くぼみに堆積される。

(もっと読む)

炭化珪素半導体装置およびその製造方法。

【課題】炭化珪素半導体装置のチャネル移動度の向上を図る。

【解決手段】 ゲート酸化膜形成工程の降温時に、ウェット雰囲気を維持したまま、終端・脱離温度(800〜900℃)以下まで降温させる。これにより、ゲート酸化膜とチャネル領域を構成するp型ベース層の界面のダングリングボンドをHもしくはOHの元素で終端させることが可能となる。このため、高いチャネル移動度の反転型ラテラルMOSFETとすることが可能となる。

(もっと読む)

半導体素子

【課題】 高い耐圧を有し且つ低いオン抵抗を有するノーマリオン型の半導体素子を提供する。

【解決手段】 ゲート電極9のドレイン層6側の端部と、チャネル領域7とドレイン層6との間の接合面との間は、距離x(x>0)がとられている。チャネル領域7は、ゲート電極9の直下の部分がチャネルとして機能し、右側の領域がドレイン層6の拡張領域として機能する。

(もっと読む)

半導体集積回路装置

【課題】微細化されたMISFETのしきい値電圧のばらつきを低減する。

【解決手段】MISFET(Q1)のゲート電極9aは、素子分離溝2によって周囲を規定されたアクティブ領域Lの基板1上に形成され、アクティブ領域Lを横切ってその一端から他端に延在している。このゲート電極9aは、アクティブ領域Lと素子分離溝2との境界領域におけるゲート長がアクティブ領域Lの中央部におけるゲート長よりも大きく、全体としてH形の平面パターンで構成されている。また、このゲート電極9aは、アクティブ領域Lと素子分離溝2との境界領域のゲート長方向に沿った一辺の全体とゲート幅方向に沿った二辺の一部とを覆っている。

(もっと読む)

半導体集積回路

【課題】ソース電位(VSS)との間に低不純物濃度のウェル領域を具備することにより、容量素子と他の回路素子との容量結合を抑制する。

【解決手段】N型の基板10上にP型のウェル領域11とN型のウェル領域12を形成する。N型ウェル領域12の表面にゲート電極14、ソース・ドレイン領域13、N型の拡散領域15を形成し、ゲート酸化膜16を誘電体として容量素子を形成する。P型のウェル領域11にはソース電位(VSS)を印加する。ゲート電極14を一方の端子Aとし、ソース・ドレイン領域13とN型の拡散領域12とを他方の端子Bとする。N型ウェル領域12とP型ウェル領域11とが低濃度PN接合となるので、他方の端子Bとソース電位(VSS)間の寄生容量を低減できる。

(もっと読む)

半導体素子およびその製造方法

【課題】半導体層表面に対する粗面やステップバンチングの形成を抑制しつつ、半導体層と電極との接触抵抗を低減する。

【解決手段】基板の表面に形成された半導体層10と、半導体層10と電気的に接触するオーミック電極5と、半導体層10の少なくとも一部を覆うゲート電極6とを備えた半導体素子であって、半導体層10の表面のうちオーミック電極5に対向する部分7の表面粗さRz1は、半導体層10の表面のうちゲート電極6に対向する部分8の表面粗さRz2よりも大きい。

(もっと読む)

パワー半導体デバイス

【課題】 パワー半導体デバイスを、通常OFF(エンハンスメントモード)デバイスとしたり、かなり低い閾値電圧を有する通常ON(空乏モード)デバイスとする。

【解決手段】 III属窒化物のパワー半導体デバイスに、段形状のヘテロ接合部を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】表面濃度が濃く且つ急峻な不純物濃度分布を有するチャネル拡散層を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜11とゲート電極12が形成され、ゲート電極12の側面上にサイドウォール13が形成されている。そして、ゲート電極12の側方下にはP型エクステンション拡散層14が形成され、サイドウォール13の側方下にはP型ソース・ドレイン拡散層15が形成されている。ゲート絶縁膜11の下側の領域には、インジウムイオンが主な不純物である第1のP型チャネル拡散層16と、ボロンが主な不純物である第2のP型チャネル拡散層17が形成されている。そして、第1のP型チャネル拡散層16の底面側を覆うように、N型拡散層18が形成されている。

(もっと読む)

Nチャネルプルアップ素子および論理回路

【課題】相補型(CMOS)集積回路におけるプルアップデバイスとしてPMOSFETの代替品となる新たな種類のnチャネルMOSFETを提供する。

【解決手段】切換可能な負性微分抵抗(SNDR)特性を有するnチャネルFETを開示している。このSNDRFETをデプリーションモードデバイスとして構成し、実質的にpチャネルデバイスとして動作するようにバイアスをかける。このデバイスはnチャネルデバイスであるから、動作速度は高く、一方、大規模回路として設計製造する際のプロセス技術の複雑性は緩和される。このデバイスはCMOSに匹敵する性能を達成するので論理ゲート(インバータに含まれるものなど)におけるpチャネルプルアップデバイスの代替品として好適である。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜における絶縁耐圧を改善して、信頼性の高い半導体装置を提供する。

【解決手段】第1半導体層42の上に形成された第2半導体層44と、第1半導体層42から電気的に絶縁されたゲート電極53と、ソース電極51およびドレイン電極55と、ゲート絶縁膜49と、少なくとも一部が第1導電型のウェル領域45の内部に形成され、ソース電極51に電気的に接触する第2導電型のソース領域47と、ドリフト領域43とを備え、第2半導体層44における所定の領域は、第2導電型層を含む蓄積チャネル領域であり、ウェル領域45の内部に形成され、かつ、ソース領域47と接する補助ソース領域48をさらに有し、ソース領域47はゲート電極53によってオーバーラップされておらず、補助ソース領域48の一部はゲート電極53によってオーバーラップされており、補助ソース領域48の総ドーズ量は、ソース領域47の総ドーズ量よりも少ない。

(もっと読む)

セルフバイアストランジスタ構造およびSRAMセル

自己バイアス半導体スイッチを供給することで、個々のアクティブコンポーネント数を減らしたSRAMセル(450)を実現することができる。特定の実施形態では、自己バイアス半導体デバイスを、ダブルチャネル電界効果トランジスタ(400)の形式で与えることができる。このトランジスタは、トランジスタ数が6つ未満の、また、好ましい実施形態では、わずか2つの個々のトランジスタ素子を備えたSRAMセル(450)の形成を可能にする。  (もっと読む)

(もっと読む)

電界効果型MOSトランジスタ

【課題】 高信頼性を実現するプロセスモニタに適したデプレッション型電界効果型MOSトランジスタを提供する。

【解決手段】 多結晶シリコン中に作製したダイオード及び半導体基板中に作製したダイオードで双方向ダイオードを形成し、この双方向ダイオードを金属配線でデプレッション型電界効果型MOSトランジスタのゲート電極と半導体基板間に接続する。

(もっと読む)

21 - 40 / 42

[ Back to top ]