Fターム[5F140AC32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 用途 (713) | メモリ (556)

Fターム[5F140AC32]に分類される特許

541 - 556 / 556

スピントランジスタ、プログラマブル論理回路および磁気メモリ

【課題】増幅機能を有するスピントランジスタを提供すること。

【解決手段】スピントランジスタ100は、半導体基板10と、半導体基板10上において第1方向に磁化された強磁性体で形成される第1導電層12と、半導体基板10上において第1方向とその第1方向に対して反平行の第2方向とのいずれか一方に磁化される強磁性体で形成された第2導電層14と、第1導電層12と第2導電層14の間に位置し、第1導電層12と第2導電層14との間で電子スピンを導くチャネル部と、チャネル部の上方に位置するゲート電極40と、第1導電層12および第2導電層14の少なくとも一方とチャネル部との間に位置するトンネルバリア膜11a,11bと、を備える。

(もっと読む)

半導体装置

【課題】 酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる半導体装置を得る。

【解決手段】 半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極上に形成された第1の窒化膜と、ゲート電極及び第1の窒化膜の側面に順番に形成された第1の酸化膜、第2の窒化膜、第2の酸化膜及び第3の窒化膜からなるサイドウォールとを有し、第1の窒化膜は、上部の外径が下部の外径よりも小さく、第1の酸化膜のゲート電極の側面にある部分は、上面から見て第2の窒化膜で覆われ、第2の酸化膜のゲート電極の側面にある部分は、上面から見て第3の窒化膜で覆われている。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

半導体装置の製造方法

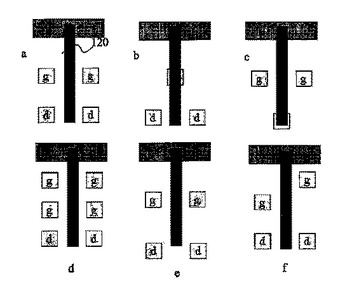

【課題】 写真製版処理で解像可能な寸法より小さな寸法の積層物を半導体基板上に形成できる半導体装置の製造方法を提供する。

【解決手段】 この半導体装置の製造方法は、半導体基板3上に写真製版処理により所定の横幅W2の積層物11aを形成する工程と、積層物11a上に第1のマスク層13を形成し、この第1のマスク層13に、エッチングにより、積層物11aの前記横幅方向に直交する方向に渡って、前記積層物11aの前記横幅方向のその開口幅W4が第1のマスク層13の上面から下面に向かってテーパ状に狭まった開口部13dを形成する工程と、第1のマスク層13をマスクとして積層物11aを開口部13dの下面開口に沿って部分的にエッチング除去することにより、積層物11aを開口部13dの下面開口に沿って分割積層物11に分割する工程とを含む。

(もっと読む)

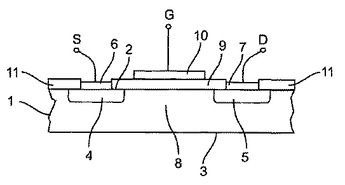

ソース/ドレイン部分絶縁部を有する電界効果トランジスタ、および、その製造方法

本発明は、ソース/ドレイン部分絶縁部を備えた電界効果トランジスタ、および、その製造方法に関するものである。間隔の空いたソース凹部(SV)とドレイン凹部(DV)とを半導体基板(1)の中に形成し、ソース・ドレイン凹部(SV・DV)の少なくとも下部領域に、凹部絶縁層(VI)を形成し、上記ソース・ドレイン凹部(SV・DV)に、導電性充填層(F)を配置することにより、ソース・ドレイン領域(S・D)を形成する。したがって、接合容量が低減された電界効果トランジスタが、ゲート誘電体(3)およびゲート層(4)とともに得られる。  (もっと読む)

(もっと読む)

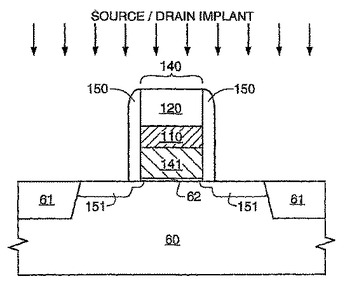

半導体素子及びその製造方法

【課題】最適なしきい電圧(Vt)が得られる半導体素子及びその製造方法を提供する。

【解決手段】本発明に係る半導体素子の製造方法は、シリコン基板上に、パッド酸化膜及びパッド窒化膜を順次形成するステップと、前記パッド窒化膜とパッド酸化膜及びシリコン基板をエッチングして素子分離領域にトレンチを形成するステップと、トレンチの側壁に絶縁膜スペーサを形成するステップと、前記絶縁膜スペーサ及びエッチングされたパッド窒化膜をエッチング障壁として横方向エッチングを行い、前記シリコン基板のアクティブ領域に空きの空間を形成するステップと、前記絶縁膜スペーサを除去するステップと、前記空間の表面上に絶縁膜を介して基板のボディ領域の電位を調節するための外部電圧が印加される導電性電極を形成するステップと、前記トレンチ内に酸化膜を埋め込みさせて素子分離膜を形成するステップと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

ソース、ドレイン、及びゲートを有する電気機械的ナノチューブトンネル装置

本発明は、長手方向及び横方向の延長部を有するナノチューブと、ナノチューブの少なくとも第1部分を支持する構造と、その横方向の延長部によって定義されている第1方向においてナノチューブに対して力を作用させる第1手段と、を有するナノチューブ装置(100)に関するものである。ナノチューブの少なくとも第2部分は、力が一定のレベルを超過した際に、ナノチューブの第2部分がその横方向の延長部の方向において曲がり、これによって第1電気回路を閉じるように、構造の支持部を超えて突出している。好適には、力をナノチューブに対して作用させる第1手段は、電気的な手段であり、この力は、電圧をこの手段に印加することによって生成される。本装置は、ソース及びドレイン電極の両方において量子力学トンネル現象を実現する。  (もっと読む)

(もっと読む)

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

541 - 556 / 556

[ Back to top ]