Fターム[5F140BB06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面から離間したチャネル (419)

Fターム[5F140BB06]に分類される特許

161 - 180 / 419

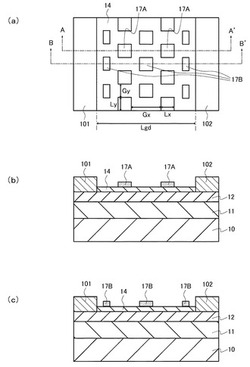

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSトランジスタのオン電流を低下させずにMOSトランジスタを小型化する。

【解決手段】素子形成領域2を他の領域と分離する素子分離領域3が形成された基板(半導体基板1)と、素子形成領域2に形成されたゲート溝4と、素子形成領域2にゲート溝4を挟んで離間して形成された一対の拡散領域5を有する。更に、ゲート溝4内及びゲート溝4の周囲縁部に形成されたゲート6を有する。ゲート溝4は、チャネル幅方向Dではその開口端4aの形状が素子分離領域3により画定され、且つ、チャネル長方向Eでは一対の拡散領域5にそれぞれ接するように形成されている。チャネル幅方向Dにおいて、ゲート溝4と素子分離領域3との間に、一対の拡散領域5を繋ぐ半導体領域(シリコン領域20)を有している。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法、半導体装置及びデータ処理システム

【課題】第1配線の比抵抗が小さく、シリサイド異常成長が抑制された半導体装置の製造方法の提供。

【解決手段】第1溝を半導体基板1に設けた後、第1溝内に、シリコンとの間でシリサイドを形成しない材料からなる導体層6と半導体層10とを含む第1配線11を形成して、半導体層と半導体基板とを直接に接触させる工程と、半導体層に含まれるドーパントを半導体基板に拡散させて第1不純物拡散領域13を形成する工程と、第1溝と交差する方向に延在する第2溝を半導体基板に設けることで、第1不純物拡散領域を包含して半導体基板に立設されたピラー部1bを形成する工程と、第2溝の側壁面にゲート絶縁膜16を形成してから、ゲート絶縁膜を介してピラー部に対向する第2配線17を第2溝内に形成する工程と、ピラー部の先端部に、第2不純物拡散領域19を形成する工程と、を具備してなる半導体装置の製造方法を採用する。

(もっと読む)

電界効果トランジスタ、半導体基板及び電界効果トランジスタの製造方法

【課題】高いチャネル移動度を有する電界効果トランジスタを提供する。

【解決手段】ゲート絶縁層と、前記ゲート絶縁層に接する第1半導体結晶層と、第1半導体結晶層に格子整合または擬格子整合する第2半導体結晶層とを有し、前記ゲート絶縁層、前記第1半導体結晶層および前記第2半導体結晶層が、ゲート絶縁層、第1半導体結晶層、第2半導体結晶層の順に配置されており、前記第1半導体結晶層がInx1Ga1−x1Asy1P1−y1(0<x1≦1、0≦y1≦1)であり、前記第2半導体結晶層がInx2Ga1−x2Asy2P1−y2(0≦x2≦1、0≦y2≦1、y2≠y1)であり、前記第1半導体結晶層の電子親和力Ea1が前記第2半導体結晶層の電子親和力Ea2より小さい電界効果トランジスタを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動電流の増大を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に線状に形成された第2部分12bと、を有する第2半導体層12と、前記第2半導体層の前記第2部分の周囲に絶縁膜17を介して形成されたゲート電極18と、を具備し、前記第2半導体層の前記第2部分の膜厚は、前記第2半導体層の前記第1部分の膜厚より小さい。

(もっと読む)

半導体構造

半導体構造(110)は、障壁層(110)、スペーサ構造(120)およびチャネル層(130)を含む。障壁層(110)は、III族窒化物を含む。スペーサ構造(120)は、第1の窒化アルミニウム層(122)、中間層(124)および第2の窒化アルミニウム層(126)を含む。中間層(124)は、III族窒化物を含み、第1の窒化アルミニウム層(122)と第2の窒化アルミニウム層(126)との間に配置される。さらに、中間層(124)は、第2の窒化アルミニウム層(126)との界面において第1の自由電荷担体密度を有する。スペーサ構造(120)は、障壁層(110)とチャネル層(130)との間に配置される。チャネル層(130)は、III族窒化物を含み、スペーサ構造(120)の第1の窒化アルミニウム層(122)との界面において第2の自由電荷担体密度を有する。第1の窒化アルミニウム層(122)、中間層(124)および第2の窒化アルミニウム層(126)は、第1の自由電荷担体密度が第2の自由電荷担体密度の10%未満であるような層厚さを有する。 (もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

フィンタイプデバイスシステム及び方法

フィンタイプデバイスシステム及び方法が開示される。特定の実施形態において、表面を有する基板内にトランジスタのゲートを形成する段階と、前記基板内に、第1BOX層面において前記ゲートに隣接する埋込酸化物(BOX)層を形成する段階と、を含むトランジスタの製造方法が開示される。本方法はまた、レイズドソース−ドレインチャネル(フィン)を形成する段階であって、前記フィンの少なくとも一部が前記基板の表面から延長し、前記フィンが、前記BOX層の第2BOX層面に隣接する第1フィン面を有する段階を含む。  (もっと読む)

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に第1窒化物半導体層、第2窒化物半導体層、および第3窒化物半導体層が順次積層された窒化物半導体積層体と、ソース電極およびドレイン電極と、第2窒化物半導体層および第3窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域の内面および窒化物半導体積層体の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含み、絶縁膜に接する第1窒化物半導体層の上面と、第2窒化物半導体層に接する第1窒化物半導体層の上面とに段差がないことを特徴とする。

(もっと読む)

チャネルを空乏化する界面電荷を有するゲート絶縁層を備えたトランジスタ及び関連した製造方法

金属−絶縁体−半導体電界効果トランジスタ(MISFET)は、第1の導電型の離間されたソース領域とドレイン領域とをその中に有するSiC層を含む。第1のゲート絶縁層は、SiC層上にあり、SiC層との界面に沿って、ソース領域の多数キャリアと同じ極性の正味の電荷を有する。ゲートコンタクトは、ソース領域とドレイン領域との間のSiC層のチャネル領域の上方の、第1のゲート絶縁層上にある。第1のゲート絶縁層とSiC層との間の界面に沿った正味の電荷は、SiC層内のソース領域とドレイン領域との間のチャネル領域の隣接部分の多数キャリアを空乏化することができ、そのことにより、MISFETの閾値電圧を上昇させ、及び/又は内部の電子移動度を高めることができる。 (もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲートを含むトランジスタにおいて、ゲート側方におけるソース・ドレイン間の短絡を防ぎ、トランジスタの動作を良好に制御する。

【解決手段】半導体装置100は、ドレイン領域106およびソース領域108の間に形成され、素子分離領域104を貫通して基板102にまで達するトレンチ内に形成されたトレンチゲート118を含む。また、平面視において、トレンチゲート118の外縁には素子分離領域104が形成されている。ここで、トレンチゲート118は、ソース領域108からトレンチゲート118の下方を介してドレイン領域106に到る第1の経路P1が、ソース領域108からトレンチゲート118の側方を介してドレイン領域106に到る第2の経路P2または第3の経路P3よりも短くなるように形成される。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたノーマリオフ型のトランジスタを備えた半導体装置において、駆動時のゲート電流を低減しつつ、トランジスタの過渡応答特性を安定させる。

【解決手段】半導体装置は、基板101と、基板101の上に積層された複数の窒化物半導体層からなり、且つチャネル領域を含む第1の窒化物半導体層104Sと、第1の窒化物半導体層104Sの上に形成され、且つチャネル領域と逆導電型の第2の半導体層105と、第2の半導体層105に接するように形成され、金属層107からなる導電層と、導電層の上に形成された絶縁体層110と、絶縁体層110の上に形成されたゲート電極111と、第2の半導体層105の両側方に形成されたソース電極108及びドレイン電極109とを備えている。

(もっと読む)

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

161 - 180 / 419

[ Back to top ]