Fターム[5F140BB19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | 超格子構造、ヘテロ構造 (487) | 量子細線 (36)

Fターム[5F140BB19]に分類される特許

1 - 20 / 36

半導体装置及びその製造方法、電源装置、高周波増幅器

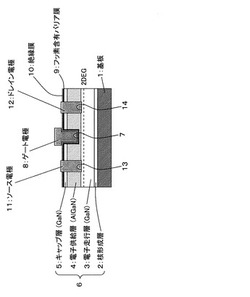

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタ

【課題】伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタを提供する。

【解決手段】本発明は、単一端子トランジスタ装置に関する。一具体例において、nチャネルトランジスタは、離散正孔準位H0を有する第一半導体層と、伝導帯底EC2を有する第二半導体層と、第一半導体層と第二半導体層の間に配置される広バンドギャップ半導体バリア層と、第一半導体層の上方のゲート誘電層と、ゲート誘電層の上方にあり、ゼロバイアスを加え、n端子特徴を得るために、離散正孔準位H0が伝導帯底Ec2の下方に位置するように選択された有効仕事関数を有するゲート金属層と、からなる。

(もっと読む)

マルチゲートIII−V量子井戸構造

マイクロ電子構造を形成する方法を記載する。方法の実施形態は、基板上にIII−Vトライゲートフィンを形成する段階と、III−Vトライゲートフィンの周囲にクラッド材を形成する段階と、クラッド材の周りに高誘電率ゲート誘電体を形成する段階とを備える。 (もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

単電子ターンスタイルデバイスおよびその製造方法

【課題】より小さな単電子島が作製でき、また、高い精度を必要とせずにトップゲートが配置できるようにする。

【解決手段】形成しようとする細線の延在方向に対して直交して開口部104を挟む2つの箇所に、対向して配置される2つの溝部105を形成する。溝部105は、絶縁層101に到達するまで形成する。次に、酸化シリコン層103を介してシリコン層102の上層部を熱酸化し、シリコン層102をより薄くする。この酸化工程により、開口部104の対向する2つの曲線状の縁部に対応する曲線状の境界部の内側近傍において、層厚方向にくびれるくびれ部107が形成され、くびれ部107においては、シリコン層102の層厚がより薄くなり、層厚方向の量子サイズ効果によりトンネルバリアが形成されるようになる。

(もっと読む)

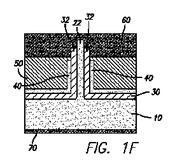

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

歪み検出素子

【課題】ゲート電極、ソース電極、およびドレイン電極を備えたトランジスタ型の歪み検出素子であって、金属製歪みゲージよりも格段に優れた検出感度を有する歪み検出素子の提供。

【解決手段】ゲート電極と、ソース電極と、ドレイン電極と、チャネルが形成される圧電材料からなる層と、を備えた歪み検出素子であって、(a)上記ゲート電極の長さが2μmより大きいこと、(b)上記ゲート電極の幅が1mmより小さいこと、(c)上記ゲート電極と上記ソース電極の距離と、上記ゲート電極と上記ドレイン電極の距離との和が13μmより大きいこと、の3条件のうち少なくともいずれか1つの条件が成立していることを特徴とする。

(もっと読む)

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られるデバイス

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られる電子構造体について記載する。こうした構造体は、金属−酸化物−半導体(MOS)構造を含むことができ、構造体はMOS電界効果トランジスタ(MOSFET)または光電子スイッチに用いることができる。  (もっと読む)

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】低いコンタクト抵抗を有し、かつ、オン抵抗の増大を回避できて高いチャネル移動度を維持できるノーマリオフ動作の電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタは、AlGaN障壁層6の薄層部6aは、第2のGaN層4のV欠陥13およびV欠陥13に連なる第3のGaN層5の非成長領域G1上に形成されているので、エッチングを行うことなく平坦部6bよりも薄くできる。よって、エッチングダメージがチャネル移動度を低下させることがなく、オン抵抗の増大を回避できる。

(もっと読む)

GaN系半導体素子およびその製造方法

【課題】SiO2からなるゲート絶縁膜を常圧CVDによって形成することで、十分なノーマリオフ特性が得られるGaN系半導体素子およびその製造方法を提供する。

【解決手段】基板11上にバッファ層13を介して積層されたp型のGaN系化合物半導体からなるチャネル層14とゲート電極Gとの間にゲート絶縁膜17が形成されたGaN系半導体素子1において、ゲート絶縁膜17が、常圧CVD法により成膜されたSiO2膜である。常圧CVD法により成膜されたSiO2膜は、Si−H結合や未結合手の発生が抑制された高品質のSiO2膜である。このようなSiO2膜により、GaN系半導体素子のしきい値の制御に及ぼす悪影響も抑制されるので、十分なノーマリオフ特性が得られる。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのリーク電流を防止できる電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタによれば、WN/Alドレイン電極109がドレイン電極109の下のn+型領域(拡散領域)112を介してGaNチャネル層104にショットキー接合されている。これにより、従来の熱処理によりドレイン電極にオーミックコンタクトを形成する場合と異なり、ドレイン電極109下へメタルが侵入することを回避できる。よって、このメタル侵入が発生するために生じるリーク電流を低減することが可能であり、電界効果型トランジスタにおける破壊電圧を向上できる。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

1 - 20 / 36

[ Back to top ]