Fターム[5F140BF10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467) | 金属 (3,194) | 金属化合物(窒化物、酸化物) (807)

Fターム[5F140BF10]に分類される特許

41 - 60 / 807

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】チャネル移動度の低下を抑制しつつ閾値電圧を制御する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(b)二酸化珪素膜が形成された炭化珪素基板を窒化処理する工程と、(c)窒化処理された炭化珪素基板を水蒸気を含んだ酸素雰囲気で熱処理する工程とを備える。工程(c)は、(c1)窒化処理された炭化珪素基板を投入した熱処理炉の温度を不活性ガス雰囲気中で昇温又は降温する工程を含む。工程(c1)は、窒化処理直後のチャネル移動度をμch、昇温又は降温開始時刻をt=0、熱処理開始時刻をt=t1、熱処理終了時刻をt=t2、熱処理炉からの基板取出時刻をt=t3、ボルツマン定数をk、時刻tにおける熱処理炉の温度をT(K)とした場合に、式(1)により求められる炭化珪素基板中のチャネル移動度の低下率が10%以下となるように昇温速度及び/又は降温速度を決定する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

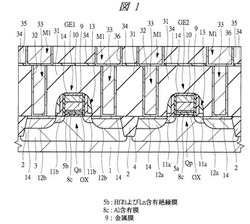

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リーク電流および閾値を低減させるゲート絶縁膜を提供する。

【解決手段】図1に示すように、半導体基板1上に、ゲート絶縁膜3を形成するゲート絶縁膜形成工程と、ゲート絶縁膜3上に、ゲート電極4を形成するゲート電極形成工程と、を備え、ゲート絶縁膜形成工程は、第1金属の酸化膜あるいは酸窒化膜を、成膜する第1の成膜工程と、第1金属の酸化膜あるいは酸窒化膜上に第2金属または、その酸化物を成膜する第2の成膜工程と、第2金属を第1金属の酸化膜中に拡散させるために熱処理する熱処理工程の3工程を含む。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

41 - 60 / 807

[ Back to top ]