Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

321 - 340 / 411

半導体装置及びその製造方法

【課題】 半導体素子の微細化にともない半導体基板の斜面を使用したMOSトランジスタにおいては、斜面の上端に近い箇所と下端に近い箇所とでゲート電極膜の膜厚が異なることになり、ドライエッチングによるパターニングが困難になるという問題点がある。

【解決手段】 斜面上にゲート電極を有するMOSトランジスタは、最初に斜面の下端に近い箇所の下層ゲート電極膜のパターニングを行う。さらにそのゲート電極間のスペースを基板の主表面まで埋設させ主表面と高さを同一とした後、上層のゲート電極膜を成膜しゲート電極膜のパターニングを行う。このためにコンタクトホール開口時のアスペクト比が小さくなり、微細パターンのパターニングが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

金属不純物の導入による導電性電極の仕事関数を変更する方法(およびその半導体構造体)

【課題】 導電性電極と高k誘電体との間に配置された金属含有材料層に少なくとも1つの金属不純物を導入することによって導電性電極スタックの仕事関数が変更される、半導体構造体を提供すること。

【解決手段】 例えば、導電性電極と共に電極スタック内に存在する金属含有材料層に金属不純物を導入することによって導電性電極スタックの仕事関数が変更される、電界効果トランジスタ(FET)及び/又は金属酸化物半導体キャパシタ(MOSCAP)のような半導体構造体である。金属不純物の選択は、電極がn型仕事関数を有するか、又はp型仕事関数を有するかによって決まる。本発明はまた、こうした半導体構造体の製造方法も提供する。金属不純物の導入は、金属含有材料及び仕事関数変更用の金属不純物の両方を含む層を共堆積して、金属不純物の層が金属含有材料層の間に存在するスタックを形成することによって、或いは、金属含有材料の上及び/又は下に金属不純物を含む材料層を形成し、次いで、構造体を加熱し、金属不純物が金属含有材料に導入されるようにすることによって、達成することができる。

(もっと読む)

半導体装置の製造方法

【課題】浅い接合領域上に、浅いニッケルモノシリサイド層を形成する。

【解決手段】絶縁膜で画成されたシリコン面上に金属ニッケル膜を堆積し、シラン雰囲気中、220℃を超えない温度で熱処理し、組成がNi2Siのシリサイド層を、接合領域との界面および金属ニッケル膜表面に、未反応の金属ニッケル膜が残るように形成した後、前記未反応の金属ニッケル膜をエッチング除去し、熱処理してニッケルモノシリサイド層に変換する。

(もっと読む)

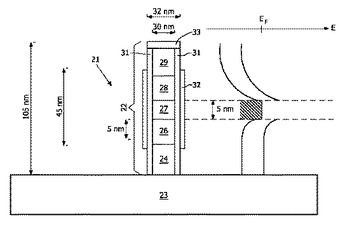

バリアを有するトンネルトランジスタ

本発明は、ソース(24)およびドレイン(29)、並びにこれらのソースとドレインの間に配置されたバリア領域(27)を備えたトランジスタ(21)を提案する。バリア領域は、半導体材料の真性または低濃度ドーピング領域(26,28)によってソースおよびドレインから分離されている。バリア領域と真性または低濃度ドーピング領域との界面にポテンシャルバリアが形成される。ゲート電極(32)はポテンシャルバリアの付近に設けられ、ゲート電極に適切な電圧を印加することによって、ポテンシャルバリアの実効的な高さおよび/または幅を調整することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の劣化特性及び電流の漏れ現象を防止することのできる半導体装置を提供する。

【解決手段】半導体基板100と、半導体基板100上に高誘電性物質で形成されるゲート絶縁膜120と、ゲート絶縁膜120上にアルミニウム合金で形成されるバリア金属膜130と、バリア金属膜130上に形成されるゲート電極層140と、を含む。バリア金属膜130は、タンタルアルミニウム窒化膜又はチタンアルミニウム窒化膜で形成される。従って、バリア金属膜を耐酸化性の大きい物質で形成することで、酸素雰囲気の中で半導体装置の後続熱処理工程中のバリア金属膜の酸化を防止し、ゲート電極の劣化特性及び電流漏れ現象を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜に接するゲート電極の空乏化を抑制しながら、ゲート電極の仕事関数の調整を効率的に行うことが可能な半導体装置およびその製造方法を提供する。

【解決手段】 p型シリコン基板1、埋め込み酸化膜2、及び単結晶シリコン層3から構成されるSOI基板4において、単結晶シリコン層3にソース領域10およびドレイン領域11を備える。また、ソース領域10とドレイン領域11との間の単結晶シリコン層3の表面側はチャネル層3aとして機能する。単結晶シリコン層3(チャネル層3a)の上にはゲート絶縁膜5が形成される。ゲート絶縁膜5上には、窒化チタン(TiN)からなる金属粒子6a,6b、及びポリシリコン膜7から構成されるポリシリコンゲート電極8が設けられる。ここで、TiNからなる金属粒子は、ゲート絶縁膜5に接する部分6aと接しない部分6bからなる。

(もっと読む)

垂直チャネルを有する半導体素子及びその製造方法

【課題】デザインルールによって制限されるチャネル長の限界を克服し、セル電流を増加させることによって、セルを安定して動作させることができる垂直チャネルを有する半導体素子及びその製造方法を提供すること。

【解決手段】表面領域、及び表面領域間に形成された底部が表面領域より低い第1リセス230Aを備えた活性領域223と、活性領域223の周囲を囲む素子分離膜222と、活性領域223と交差する方向に、活性領域223の表面領域上を横切るように形成された少なくとも1対のゲートライン227と、ゲートライン227の下部の素子分離膜222に形成され、ゲートライン227の一部が埋め込まれた第2リセス225と、

第1リセスの底部の活性領域223に形成された第1接合領域と、ゲートライン227の外側の表面領域に形成され、第1接合領域との間に垂直チャネルを構成する第2接合領域を備える。

(もっと読む)

pFET材料としての金属酸窒化物を用いた半導体構造およびその製造方法

【課題】高k誘電体を含むゲート・スタック上において熱に対して安定な新規の金属化合物であって、金属炭化物の場合に起こるような炭素拡散を引き起こさない金属化合物を提供すること。

【解決手段】仕事関数が約4.75から約5.3、好ましくは約5eVであるp型金属であり、高k誘電体とインタフェース層とを含むゲート・スタック上で熱に対して安定なMOxNyを含む金属化合物、およびこのMOxNy金属化合物を製作する方法が提供される。さらに、本発明のMOxNy金属化合物は、1000℃において非常に効率的な酸素拡散障壁であり、p金属酸化物半導体(pMOS)デバイスにおいて、非常に攻撃的な等価酸化膜厚(EOT)および14Å未満の反転層厚を可能にする。上式で、Mは元素周期表のIVB、VB、VIBまたはVIIB族から選択された金属、xは約5から約40原子%、yは約5から約40原子%である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の下部に(垂直に対して)大きな角度でイオン注入可能な半導体装置の製造方法を提供することを課題とする。また、短チャネル効果抑制の効果を損なうことなく、半導体層下部の空乏化を促進可能な半導体装置の製造方法を提供することを他の課題とする。

【解決手段】 本発明に係る半導体装置の製造方法は、半導体層上にゲート絶縁膜を形成する工程と;前記ゲート絶縁膜上に第1ゲート電極層を形成する工程と;前記第1ゲート電極層の下方にポケットイオン領域を形成する工程と;前記ポケットイオン領域の形成後に、前記第1ゲート電極層の上に第2ゲート電極層を重ねて形成する工程とを含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造方法が容易なデュアルメタルゲート構造を実現することができ、CMOSデバイス等の特性向上に寄与する。

【解決手段】 基板上に、pチャネルMISトランジスタ51とnチャネルMISトランジスタ52を具備した半導体装置であって、pチャネルMISトランジスタ51のゲート電極32の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は80%以上であり、nチャネルMISトランジスタ52のゲート電極53の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は60%以下である。

(もっと読む)

ひずみシリコンCMOS装置

【課題】半導体装置における二重応力ライナーの圧縮部分と引張り部分との間の境界を制御する改善された方法を提供する。

【解決手段】境界は、Nウェル302境界360,361,362,363により決められるのではなく、チャネルやアクティブ領域301の境界といったPFETフィーチャから測られるような所定距離により位置されるよう適切に設計することができる。これは、PFET350性能を改善および/または整合する機会を与えることができる。二重応力ライナーの圧縮部分305と引張り部分との間の境界を適切に設計することにより、PFET上の圧縮応力を、x方向に維持するかさらに増加しながらy方向に減少することができ、PFET性能を改善することが可能になる。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】ウォーターマークの発生を抑制することができる半導体装置を提供する。

【解決手段】本発明の半導体装置は、シリコン基板上に、ゲート絶縁膜と、高濃度リンドープポリシリコン膜及び上層ポリシリコン膜とからなるゲート電極とを順次備え、上層ポリシリコン膜中でのリン濃度は、高濃度リンドープポリシリコン膜から離れるにつれて低下することを特徴とする。

(もっと読む)

プラズマエッチング方法

【課題】高誘電率絶縁体からなる絶縁材料層上に形成した遷移金属元素を含む電極材料層に対し高選択比でエッチングを施すことのできるエッチング技術を提供する。

【解決手段】遷移金属元素を含む電極材料層107および高誘電率絶縁体108からなる絶縁材料層の積層体を備えた試料を真空処理容器内に設置した下部電極上に配置し、前記真空処理容器内に処理ガスを導入し、前記真空処理容器内に高周波電力を供給して前記導入した処理ガスをプラズマ化して前記試料表面にエッチング処理を施すプラズマエッチング処理方法において、前記電極材料層をエッチングするとき、処理ガスとしてHClガスを供給する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10において、ソース領域40およびドレイン領域50が形成された半導体基板30と、ソース領域40およびドレイン領域50に挟まれた半導体基板30上に形成された絶縁膜60と、絶縁膜60上に形成されたゲート電極80と、絶縁膜60とゲート電極80との界面に形成された金属含有粒子70と、金属含有粒子70のうち界面の縁部60aからはみ出していた金属含有粒子が変化した絶縁粒子72と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】シリコン系材料、例えばシリコン基板、多結晶シリコンパターン等をドライエッチングする際の前処理のエッチングに、フッ化水素とアンモニアとからなるエッチングガスを用いることで、自然酸化膜を選択的に除去することを可能とする。

【解決手段】酸化シリコン(素子分離領域12、サイドウォール18、19等)と表面に自然酸化膜21、22が形成されたシリコン系材料(シリコン基板11)とが露出された状態で自然酸化膜21、22を除去する工程と、自然酸化膜21、22が除去されたシリコン系材料(シリコン基板11)をエッチング加工する工程とを備えた半導体装置の製造方法であって、自然酸化膜21、22を除去する工程は、エッチングガスにフッ化水素とアンモニアとを用いたドライエッチングにより行うことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト不良を防止しつつ応力膜を用いて効果的にチャネル形成領域に応力を印加することにより、MISFETの駆動力の向上を図る。

【解決手段】半導体基板1上に形成されたMISFETのゲート電極部20n及び20pの側面上には絶縁性のサイドウォールスペーサ9が形成されている。ゲート電極部20n及び20pの高さは、それぞれの側面上に設けられたサイドウォールスペーサ9の上端より低い。MISFET上にゲート電極部20n及び20pを覆うように、チャネル形成領域に応力を発生させる応力膜13が形成されている。応力膜13におけるゲート電極部20n及び20p上に形成されている部分の膜厚が、その他の部分の膜厚よりも厚い。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、ゲート絶縁膜との密着性に優れ、PMOSFETに適した閾値電圧が得られる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えたp型の電界効果トランジスタからなる半導体装置であって、ゲート電極15は、少なくともゲート絶縁膜14側がルテニウムとシリコンとを含む膜で構成されていることを特徴とする半導体装置である。また、ゲート電極15を形成する工程では、堆積法により、少なくともゲート絶縁膜14側にルテニウムとシリコンとを含む膜を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体構造およびその形成方法(応力付加膜によりN型MOSFETおよびP型MOSFET双方の性能を向上させる方法および構造)

【課題】p型MOSFETデバイスのチャネル内に圧縮応力をもたらし、n型MOSFETデバイスのチャネル内に引張応力をもたらす応力層が、各々のゲート・スタックに重ねられている、隣接するp型MOSFETデバイスおよびn型MOSFETデバイスを含む構造および製造方法を提供すること。

【解決手段】p型MOSFETデバイスまたはn型MOSFETデバイスのうちの一方が、隣接する他方のデバイスの高さよりも低い高さを有し、2つのデバイスのうちの低い方が、低い方のデバイスに重ねられた応力層内の不連続部すなわち開口部によって境界が画定されている。デバイスを形成するための好ましい一方法では、ゲート・スタック下の基板内に第1のタイプの応力を形成するために、異なる高さを有するゲート・スタック上に単一の応力層が形成され、第2のタイプの応力が低い方のゲート・スタックの下に形成されるように、低い方のゲート・スタックからある距離のところの応力層内に開口部が形成される。

(もっと読む)

半導体デバイス用の自己整合ショットキー接合の形成方法

半導体デバイスに対し、自己整合ショットキー接合(29)を形成する方法である。ゲートエッチング及びスペーサ形成の後、接合領域を画成する凹所を半導体基板(10)に形成し、そこに、SiGe層(22)を選択的に成長させる。その後、誘電体層(24)をゲート(14)及びSiGe層(22)の上に設け、コンタクトエッチングを行って、コンタクトホール(26)を形成してから、SiGeの材料(22)を除去して、接合領域にキャビティ(28)を作成する。最後に、キャビティ(28)を金属で満たして、接合(29)を形成する。このようにして、抵抗率が比較的低く、形状及び位置を良好に制御することができる、ショットキー接合を自己整合で形成する方法が提供される。  (もっと読む)

(もっと読む)

321 - 340 / 411

[ Back to top ]