Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

341 - 360 / 411

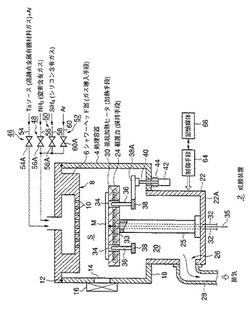

成膜方法、成膜装置及び記憶媒体

【課題】炭素濃度を十分に高くすることが可能な高融点金属の金属化合物膜よりなる薄膜を形成することが可能な成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器4内に、高融点金属有機材料ガスと窒素含有ガスとを供給して被処理体の表面に高融点金属の金属化合物膜よりなる薄膜を形成する成膜方法において、前記薄膜中に含まれる炭素濃度を高めるために前記窒素含有ガスの分圧を、全圧の10%以下となるように設定して成膜工程を行うようにする。これにより、炭素濃度を十分に高くし、トランジスタのゲート電極の閾値を低減させる。

(もっと読む)

エッチング液およびそれを用いた半導体装置の製造方法

【課題】ゲート絶縁膜の材料としてHf酸化物系のHigh−k膜を用いるとともにゲート電極の材料として金属を用いた場合においても、High−k膜のエッチングの際のゲート電極の損傷を防ぐことが可能なエッチング液およびそれを用いた半導体装置の製造方法を提供する。

【解決手段】TiN層31、Poly−Si層32、およびW層33からなるゲート電極30をドライエッチングで形成した後に、エッチング液を用いたウェットエッチングを行うことにより、SiO2層21およびHfSiO層22からなるゲート絶縁膜20を形成する。このエッチング液は、HF分子の解離を抑制する緩衝剤およびpH値を上げるpH調整剤を含有している。

(もっと読む)

トランジスタ、およびその製造方法

【課題】CMOSデバイス設計に適した仕事関数をもつメタルゲート電極を提供する。

【解決手段】

トランジスタおよびその製造工程が開示されている。相補型金属酸化膜半導体(CMOS)デバイスは、第1の厚さを有する第1ゲート電極を含むPMOSトランジスタと、第2の厚さを有する第2ゲート電極を含むNMOSトランジスタとを含み、第1の厚さは、第2の厚さよりも大きい。第1ゲート電極および第2ゲート電極は、同じ材料を含んでいることが好ましく、例として、TiSiN、TaNまたはTiNを含んでいるとよい。第1ゲート電極および第2ゲート電極の厚さによって、PMOSトランジスタおよびNMOSトランジスタの仕事関数が設定される。

(もっと読む)

トレンチトランジスタの形成方法及び該当するトレンチトランジスタ

【課題】微細化トレンチゲートMOSトランジスタの形成方法を提供する。

【解決手段】第1導電型の半導体基板に、トレンチ5を形成し、ゲート誘電体20をトレンチ5内に形成し、第1導電性充填材料30'をトレンチ5内にゲート電極30として設け、第1ソース及びドレイン領域4を、第2導電型の不純物をトレンチ5横の基板1の表面に導入することにより形成し、トレンチ5内の第1導電性充填材料30'を、所定の深さの位置まで後退するようにエッチバックし、第2ソース及びドレイン領域4'を、第2導電型の不純物をトレンチ5内の基板1の表面に導入し、絶縁スペーサ25;25'をトレンチ5内の第1導電性充填材料30'の上に形成し、第2導電性充填材料30''をトレンチ5内にゲート電極の上側部分として設ける工程と、を含む。

(もっと読む)

半導体装置

【課題】High-k絶縁膜をゲート絶縁膜として使用する電界効果トランジスタを含む半導体装置であって、メタルゲート電極化を行わずに、フェルミレベルピニングに起因するしきい値電圧固定を抑制可能な半導体装置を実現する。

【解決手段】Pチャネル型電界効果トランジスタ4において、High-k絶縁膜たる金属酸化物(好ましくは、ハフニウム酸化物(HfO2やHfSiON、HfSiO4など)またはジルコニウム酸化物(ZrO2やZrSiON、ZrSiO4など))を有するゲート絶縁膜6bと、ポリシリコンゲート電極7との間に窒化チタン(TiN)膜8を形成する。窒化チタン膜は、金属酸化物を有するゲート絶縁膜に接して形成されてもフェルミレベルピニングが起きない。また、ポリシリコンゲート電極の下部が窒化チタン膜との金属膜となっているので、ゲートの空乏化が抑止でき、電流駆動能力向上も図れる。

(もっと読む)

半導体装置

【課題】 リーク電流を減らすことを可能にするとともにフラットバンド電圧がシフトするのを抑制することを可能にする。

【解決手段】 半導体基板2上に設けられた酸素を含む高誘電体からなるゲート絶縁膜4と、ゲート絶縁膜上に設けられ、酸素を含む電気伝導体からなる電気伝導体膜6と、電気伝導体膜上に設けられたゲート電極8と、を備えている。

(もっと読む)

自己整合トレンチ分離を用いた電界低減DMOS

電子デバイスの製造方法および結果として生じる電子デバイスを提供する。方法は、シリコン・オン・インシュレータ基板(201、203、205)の最上の側にゲート酸化物(217)を形成するステップと、ゲート酸化物(217)の上に第1のポリシリコン層(219)を形成するステップと、第1のポリシリコン層(219)の上に第1の二酸化シリコン層(221)を形成するステップとを備える。そして第1の二酸化シリコン層(221)の上に第1の窒化シリコン層(223)を形成し、続いて第2の二酸化シリコン層を形成する。先の誘電体層のすべてを貫通してSOI基板(201、203、205)内へ浅いトレンチをエッチングする。エッチングされたトレンチを他の誘電体層(たとえば二酸化シリコン)(239)で充填し、平坦化する。先の誘電体層の各々を除去し、誘電体層の最上側壁区域を、後で適用されるポリシリコンゲート区域との接触のために露出させておく。側壁区域の形成によりフィールド酸化物の全厚みが保証され、それによって、電界が低減され、かつゲート領域とドリフト領域との間のキャパシタンスが低減されたデバイスが生成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜のSiO2換算膜厚の薄膜化を達成した半導体装置を提供する。

【解決手段】 半導体基板と、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、アモルファスもしくは多結晶のSi1-xGex(0≦x<0.25)を主成分とし、シリコン原子を置換する配置にあるようなp型不純物を含有するゲート電極とを具備する半導体装置である。前記ゲート電極における前記シリコン原子を置換する配置にあるようなp型不純物は、5×1019個/cm3以上5×1020個/cm3以下の濃度で含有された第一のp型不純物と、前記第一のp型不純物より原子半径が小さい第二のp型の不純物とを含み、しかも第一のp型不純物と第二のp型不純物とが共有結合していることを特徴とする。

(もっと読む)

MOS構造を有する半導体装置およびその製造方法

【課題】製造プロセスを煩雑にすることなく、閾値が異なるMOS構造のそれぞれのゲート電極に適した材料を採用して閾値を適切に制御でき、かつゲート電極からチャネル領域への拡散を顕著としない技術を提供する。

【解決手段】PMOSトランジスタQPはゲート電極GP及びこれとゲート絶縁膜5を介して対峙するN型ウェル31を、NMOSトランジスタQNはゲート電極GN及びこれとゲート絶縁膜5を介して対峙するP型ウェル32を、それぞれ有している。ゲート電極GNは多結晶シリコン層63で構成される一方、ゲート電極GPは金属層64/多結晶シリコン層63の積層構造を備えている。

(もっと読む)

MOS構造を有する半導体装置およびその製造方法

【課題】製造プロセスを煩雑にすることなく、閾値が異なるMOS構造のそれぞれのゲート電極に適した材料を採用して閾値を適切に制御でき、かつゲート電極からチャネル領域への拡散を顕著としない技術を提供する。

【解決手段】PMOSトランジスタQPはゲート電極GP及びこれとゲート絶縁膜5を介して対峙するN型ウェル31を、NMOSトランジスタQNはゲート電極GN及びこれとゲート絶縁膜5を介して対峙するP型ウェル32を、それぞれ有している。ゲート電極GNは金属層642/多結晶シリコン層63で構成される一方、ゲート電極GPは金属層641/多結晶シリコン層63の積層構造を備えている。金属層642は金属層641よりも薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】 しきい値電圧のばらつきの少ないゲート電極を有するCMOSデバイスを備えた半導体装置を提供することを可能にする。

【解決手段】 半導体基板に設けられた第1導電型チャネルMISトランジスタと、半導体基板に設けられた第2導電型チャネルMISトランジスタと、を備え、第2導電型チャネルMISトランジスタのゲート電極中の、ゲート絶縁膜との界面から膜厚方向に少なくとも1nm以下の領域での酸素濃度は1020cm−3以上、1022cm−3以下である。

(もっと読む)

MOSトランジスタを備える半導体素子及びその製造方法

【課題】MOSトランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】第1導電型の第1チャンネルが形成される第1MOSトランジスタ、及び第1導電型とは異なる第2導電型の第2チャンネルが形成される第2MOSトランジスタを有するCMOSトランジスタを備える半導体素子において、第1MOSトランジスタは、第1ゲート絶縁膜、及び第1ゲート絶縁膜上に形成され、第1金属と第2金属との合金からなる第1金属合金層を備える第1ゲート電極を備える半導体素子である。

(もっと読む)

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】薄いニッケル膜を用いてシリコンゲルマニウム層をシリサイド化する場合であっても、シート抵抗の上昇や接合リーク電流の増加を抑制し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板34上にゲート電極54pを形成する工程と、ゲート電極の両側の半導体基板内にソース/ドレイン拡散層64pを形成する工程と、ソース/ドレイン拡散層にシリコンゲルマニウム層100bを埋め込む工程と、シリコンゲルマニウム層の上部にアモルファス層101を形成する工程と、アモルファス層上にニッケル膜66を形成する工程と、熱処理を行い、ニッケル膜とアモルファス層とを反応させることにより、シリコンゲルマニウム層上にシリサイド膜102bを形成する工程とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 STI構造の沈み込みを抑制できる素子分離構造を提供する。

【解決手段】 素子分離溝の少なくとも上部を、ビスターシャリブチルアミノシランを原料とした減圧CVD法により形成されたSiOCNあるいはSiCNよりなるHF耐性膜で充填する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜のリーク電流の発生やゲート酸化膜の耐電圧性の低下を抑制するこ

とができる、信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板と前記半導体シリコン基板上にゲート酸化膜を介して設

けられたゲート配線と、を備えた半導体装置であって、

前記ゲート配線は、ゲート電極、前記ゲート電極に接して設けられたゲート配線上部構

造、ならびに側壁スペーサを有し、

前記側壁スペーサは一種もしくは二種以上の無機化合物絶縁層からなり、

かつ、前記無機化合物絶縁層の少なくとも一種は、窒素含有率が30〜70%の範囲で

あるシリコンオキシナイトライドからなることを特徴とする半導体装置。

(もっと読む)

多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタ、これを採用するCMOS集積回路素子及びその製造方法

【課題】多重仕事関数金属窒化物ゲート電極を有するMOSトランジスタが提供される。

【解決手段】MOSトランジスタは半導体基板及び前記半導体基板上に配置された中心ゲート電極を具備する。前記中心ゲート電極は金属窒化物からなる。前記中心ゲート電極の両側壁上にそれぞれソース側ゲート電極及びドレイン側ゲート電極が提供される。前記ソース/ドレイン側ゲート電極は窒素よりも小さい電気陰性度を有する第1不純物または窒素よりも大きい電気陰性度を有する第2不純物を含むドープ金属窒化物からなる。前記MOSトランジスタを採用するCMOS集積回路素子及びその製造方法も提供される。

(もっと読む)

NANDゲート回路及びダイナミック回路

【課題】バルク半導体を用いて簡単な構造で微細化と高性能化を可能としたトランジスタを持つNANDゲート回路及びダイナミック回路を提供する。

【解決手段】ソース及びドレイン拡散層は、低抵抗領域とこれより低不純物濃度で浅い拡張領域とから構成される。ソース及びドレイン拡散層の間のチャネル領域には、第1導電型の第1の不純物ドープ層と、この第1の不純物ドープ層の下に形成された第2導電型の第2の不純物ドープ層と、この第2の不純物ドープ層の下に形成された第1導電型の第3の不純物ドープ層とが形成され、第1の不純物ドープ層は、その接合深さがソース及びドレイン拡散層の拡張領域のそれと同じかより浅く設定され、第2の不純物ドープ層は、第1及び第3の不純物ドープ層との間に生じるビルトインポテンシャルにより完全空乏化するように不純物濃度と厚さが設定される。

(もっと読む)

半導体装置の製造方法

【課題】シリコン酸化膜中に導入する窒素の窒素濃度及び偏析位置を制御する工程を有する半導体装置の製造方法を提供する。

【解決手段】半導体装置18の製造方法は、基板10上にシリコン酸化膜12を形成するシリコン酸化膜形成工程1と、シリコン酸化膜12上にシリコン膜14を形成する工程(シリコン膜形成工程2)と、シリコン膜12が最表面に形成された基板10に対して熱窒化処理を行うことにより、シリコン酸化膜12中に窒素を導入する工程(熱窒化処理工程3)とを有する。

(もっと読む)

低融点材料で形成する拡張部を備える半導体デバイス

第1の半導体材料からなる基板(100)の表面(S)に沿って形成したゲート電極(1)とゲート絶縁層(2)とを備える半導体デバイスであり、ゲート電極(1)とゲート絶縁層(2)はいずれもスペーサ(3)に囲まれている。本デバイスはまた、それぞれ基板表面より下でゲート電極(1)の2つの対辺に沿って位置するソース領域(4)とドレイン領域(5)とを備える。ソース領域とドレイン領域は各々、基板(100)上に配置され、基板(100)とスペーサ(3)との間で延在する第2の半導体材料からなる部分(6,7)を備える。第2の材料の融点は、第1の材料の融点を下回る。第2の材料からなる部分(6,7)は、ソース(4)およびドレイン(5)領域の拡張部を成す。本半導体デバイスは、MOSトランジスタとすることができる。  (もっと読む)

(もっと読む)

341 - 360 / 411

[ Back to top ]